18EC33

# Third Semester B.E. Degree Examination, Jan./Feb. 2021 **Electronic Devices**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

- Write the figures of the resulting orbitals when isolated atoms brought together and explain the characteristics.

- Obtain the relationship between mobility and hall coefficient in a p-type bar placed in a magnetic field in the Z-direction. (10 Marks)

### OR

- Derive the equation which relates current density and mobility in a semiconductor in an 2 applied electric field.

- A silicon bar  $2\mu m$  long and  $200\mu m^2$  in cross sectional area is doped with  $1.5 \times 10^{17} / cm^3$ phosphorus. Find the current at 300K with 30V applied voltage. How long does it take an average electron to drift 2µm in pure silicon at an electric field of 80V/cm? Also calculate the time required at 10<sup>5</sup>V/cm. Assume mobility of electrons is 0.1350m<sup>2</sup>/Vsec. Also assume that saturation of electron drift velocity for silicon is 10<sup>7</sup> cm/s for the electric field above 10<sup>5</sup> V/cm.

- Show the effect of bias at a pn junction on transition region width, electric field, electrostatic potential, energy band diagram partic flow and current direction under the following conditions:

- Equilibrium ii) Forward bias

- iii) Reverse bias.

- (10 Marks)

- Illustrate the care and issues to be considered in the design of solar cells.

- (10 Marks)

- Explain Avalanche break down and obtain equation for the electron multiplication factor.

- Derive the relationship between the open circuit voltage and optic generation rate starting from the expression for the optically generated illuminated pn junction. (10 Marks)

### Module-3

- Show the hole and electron flow in a pnp transistor with proper biasing. (08 Marks)

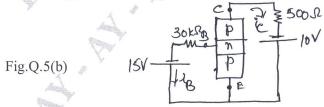

- For the circuit shown in Fig.Q.5(b) calculate  $\beta$ ,  $I_B$  and  $I_C$ . Given that  $\tau_p$  =18 $\mu$ s, and  $\tau_t$ = 0.2 $\mu s$ . What happens to the output current when  $I_B$  increases and  $\beta$  increases?

(06 Marks)

Explain the concept of base narrowing in a  $p^+ - n - p^+$  transistor.

(06 Marks)

### OR

Obtain the Ebers-Moll equations and represent the same in the model form. (12 Marks) Describe the switching effects in a CE transistor circuit. (08 Marks)

### Module-4

- Analyze the effect on gate-to-channel-space charge region and IV characteristics for the following conditions in a JFET:

- Zero gate voltage of a small drain voltage

- Zero gate voltage of a large drain voltage ii)

- Small V<sub>DS</sub> value and small reverse-biased gate voltage. iii) (10 Marks)

- Draw the energy band diagram in an MOS capacitor structure for the following cases:

- i) p-type substrate for a positive gate bias

- ii) p-type substrate for a large positive gate bias

- n-type substrate for a positive gate bias. iii)

(10 Marks)

### OR

- Write the small signal equivalent circuit of a JFET, ideal low frequency small signal equivalent circuit and ideal equivalent circuit including r<sub>s</sub>. (10 Marks)

- Show the channel formation in the MOS structure and I<sub>D</sub> versus V<sub>DS</sub> curve for the following cases:

- $V_{gs} > V_t$  and small  $V_{DS}$  value i)

- ii)

- $V_{gs}^{S} > V_{t}$  and large  $V_{DS}$  value  $V_{gs} > V_{t}$  and  $V_{DS} = V_{DS}$  (sat)

(10 Marks)

#### Module-5

- What are the fabrication steps used in the fabrication of pn junctions? (10 Marks) (10 Marks)

- With figures, describe the complementary MOS structure.

- Illustrate the evolution of integrated circuits. (10 Marks) (10 Marks)

- Explain the formation of resistors in integrated circuits