# RADIATION EFFECTS IN SEMICONDUCTORS

### Devices, Circuits, and Systems

**Series Editor**

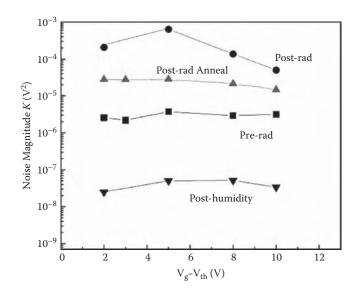

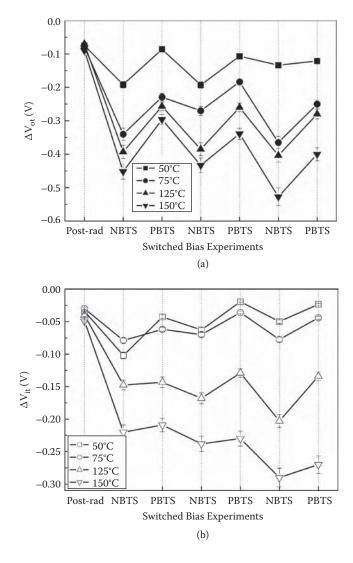

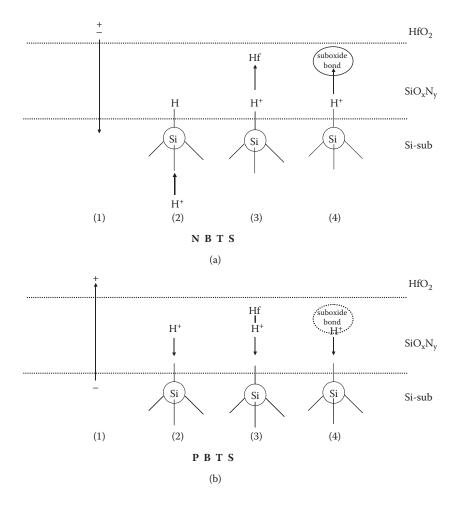

Krzysztof Iniewski CMOS Emerging Technologies Inc., Vancouver, British Columbia, Canada

Internet Networks: Wired, Wireless, and Optical Technologies Krzysztof Iniewski

> Semiconductor Radiation Detection Systems Krzysztof Iniewski

> > Electronics for Radiation Detection Krzysztof Iniewski

Radiation Effects in Semiconductors Krzysztof Iniewski

#### FORTHCOMING

Radio Frequency Integrated Circuit Design Sebastian Magierowski

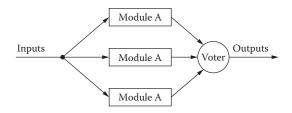

Semiconductors: Integrated Circuit Design for Manufacturability Artur Balasinki

Electrical Solitons: Theory, Applications, and Extensions in High Speed Electronics David Ricketts

Integrated Microsystems: Materials, MEMs, Photonics, Bio Interfaces Krzysztof Iniewski

# RADIATION EFFECTS IN SEMICONDUCTORS

Edited by Krzysztof Iniewski

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business

MATLAB<sup>\*</sup> is a trademark of The MathWorks, Inc. and is used with permission. The MathWorks does not warrant the accuracy of the text or exercises in this book. This book's use or discussion of MATLAB<sup>\*</sup> software or related products does not constitute endorsement or sponsorship by The MathWorks of a particular pedagogical approach or particular use of the MATLAB<sup>\*</sup> software.

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2011 by Taylor and Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number: 978-1-4398-2694-2 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright. com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

| Library of Congress Cataloging-in-Publication Data                                 |  |  |  |

|------------------------------------------------------------------------------------|--|--|--|

| Radiation effects in semiconductors / editor, Krzysztof Iniewski.                  |  |  |  |

| p. cm (Devices, circuits, and systems)                                             |  |  |  |

| Includes bibliographical references and index.                                     |  |  |  |

| ISBN 978-1-4398-2694-2 (hardcover : alk. paper)                                    |  |  |  |

| 1. SemiconductorsEffect of radiation on. 2. Photon emission. I. Iniewski, Krzyszto |  |  |  |

| II. Title. III. Series.                                                            |  |  |  |

| TK7871.85.R317 2010                                                                |  |  |  |

2010011811

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

621.3815'2--dc22

and the CRC Press Web site at http://www.crcpress.com

### Contents

| Preface              | ix   |

|----------------------|------|

| About the Editor     | xi   |

| List of Contributors | xiii |

| List of Contributors | лш   |

### SECTION I Devices

| Chapter 1 | Radiation Damage in Silicon                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Gianluigi Casse                                                                                                                                                                      |

| Chapter 2 | Radiation-Tolerant CMOS Single-Photon Imagers for<br>Multiradiation Detection                                                                                                        |

|           | Edoardo Charbon, Lucio Carrara, Cristiano Niclass,<br>Noémy Scheidegger, and Herbert Shea                                                                                            |

| Chapter 3 | Effects of Hydrogen on the Radiation Response of Field-Oxide Field-Effect Transistors and High- <i>K</i> Dielectrics                                                                 |

|           | Xing J. Zhou, Daniel M. Fleetwood, and Ronald D. Schrimpf                                                                                                                            |

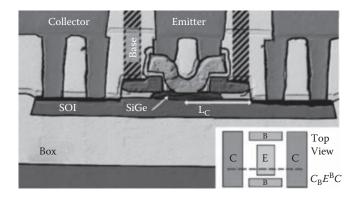

| Chapter 4 | Novel Total Dose and Heavy-Ion Charge Collection Phenomena<br>in a New SiGe HBT on Thin-Film SOI Technology69                                                                        |

|           | Grégory Avenier, Marco Bellini, Alain Chantre, Peng Cheng,<br>Pascal Chevalier, John D. Cressler, Ryan M. Diestelhorst,<br>Paul W. Marshall, Stanley D. Phillips, and Marek Turowski |

| Chapter 5 | Radiation-Hard Voltage and Current References in Standard<br>CMOS Technologies91                                                                                                     |

|           | Vladimir Gromov and Anne-Johan Annema                                                                                                                                                |

| Chapter 6 | Nanocrystal Memories: An Evolutionary Approach to Flash<br>Memory Scaling and a Class of Radiation-Tolerant Devices                                                                  |

|           | Cosimo Gerardi, Andrea Cester, Salvatore Lombardo,<br>Rosario Portoghese, and Nicola Wrachien                                                                                        |

### SECTION II Circuits and Systems

| Chapter 7  | Radiation Hardened by Design SRAM Strategies for TID and SEE Mitigation                                                                                                                                      | 51 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | Lawrence T. Clark                                                                                                                                                                                            |    |

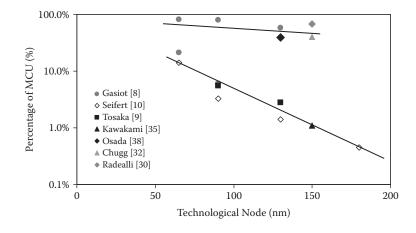

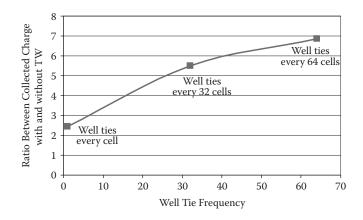

| Chapter 8  | A Complete Guide to Multiple Upsets in SRAMs Processed in<br>Decananometric CMOS Technologies                                                                                                                | 95 |

|            | Gilles Gasiot and Phillippe Roche                                                                                                                                                                            |    |

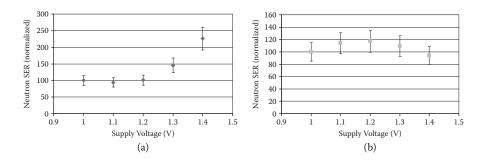

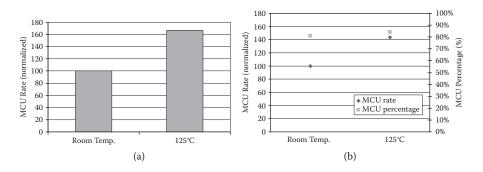

| Chapter 9  | Real-Time Soft Error Rate Characterization of Advanced SRAMs                                                                                                                                                 | 25 |

|            | Jean-Luc Autran, Gilles Gasiot, Daniela Munteanu,<br>Philippe Roche, and Sébastien Sauze                                                                                                                     |    |

| Chapter 10 | Fault Tolerance Techniques and Reliability Modeling for<br>SRAM-Based FPGAs                                                                                                                                  | 19 |

|            | Keith S. Morgan, Michael Caffrey, James Carroll, Derrick<br>Gibelyou, Paul Graham, William Howes, Jonathan Johnson,<br>Daniel McMurtrey, Patrick Ostler, Brian Pratt, Heather Quinn,<br>and Michael Wirthlin |    |

| Chapter 11 | Assuring Robust Triple Modular Redundancy Protected<br>Circuits in SRAM-Based FPGAs                                                                                                                          | 73 |

|            | Michael Caffrey, Paul Graham, Jim Krone, Kevin Lundgreen,<br>Keith S. Morgan, Brian Pratt, and Heather Quinn                                                                                                 |    |

| Chapter 12 | SEU/SET Tolerant Phase-Locked Loops                                                                                                                                                                          | )5 |

|            | Robert L. Shuler, Jr.                                                                                                                                                                                        |    |

| Chapter 13 | Autonomous Detection and Characterization of<br>Radiation-Induced Transients in Semiconductor Integrated<br>Circuits                                                                                         | 25 |

|            | Balaji Narasimham, Bharat L. Bhuva, Ronald D. Schrimpf,<br>Lloyd W. Massengill, William Timothy Holman, and<br>Arthur F. Witulski                                                                            |    |

#### Contents

| Chapter 14 | Soft Errors in Digital Circuits: Overview and Protection<br>Techniques for Digital Filters | 357 |

|------------|--------------------------------------------------------------------------------------------|-----|

|            | Pedro Reviriego Vasallo and Juan Antonio Maestro                                           |     |

| Chapter 15 | Fault-Injection Techniques for Dependability Analysis: An<br>Overview                      | 385 |

| Index      |                                                                                            | 405 |

### Preface

The need to understand radiation effects and to combat potential radiation damage in semiconductor devices and circuits has been growing in recent years. Space applications, nuclear physics, and military operations in radiation environments are obvious areas where radiation damage can have serious consequences. In addition, modern silicon processing techniques introduce radiation damage. Last, but not least, radiation is used heavily in medical imaging, from simple X-ray examinations to complex CT or SPECT/PET scanning procedures.

The interaction of radiation with matter is a very broad and complex topic. In this book we try to analyze the problem, with the aim of explaining the most important aspects for comprehending the degradation effects observed in semiconductor devices, circuits, and systems when they are irradiated. The manner in which radiation interacts with solid materials depends on the type of incident particle and on the atomic number and density of the target material. Photons interact with matter in three different ways.

- Photoelectric effect: The incident photon ionizes the target atom and is completely absorbed. A photoelectric electron is emitted and an electron in an outer orbit of the atom falls into the spot vacated by the photoelectron, causing a low-energy photoelectric photon to be emitted.

- Compton effect: An electron of the target atom is set free and a photon is emitted. The energy of the incident photon is divided between the two products of the interaction.

- Creation of electron-positron pairs: The incident photon is completely annihilated. This phenomenon never happens when the energy of the incident photon is less than 1.024 MeV.

The probability of these three effects occurring changes with the energy of the incident photon and also depends on the atomic number of the target.

The effects of photons on matter can be grouped into two classes: ionization effects and nuclear displacement. These phenomena may be caused directly by the incident particle or from secondary phenomena induced by it. Ionization in a semiconductor or insulating material creates electron-hole pairs. The number of pairs created is proportional to the quantity of energy deposited in the material that is expressed through the total absorbed dose.

This book is a must-read for anyone serious about understanding radiation effects in the electronics industry. It is aimed at post-graduate researchers, semiconductor engineers, and nuclear and space engineers with some electronics background. Emerging detector technologies, circuit design techniques, new materials, and innovative system approaches are explored by top-notch international experts in industry and academia. The book can be used as recommended reading and supplementary material in a graduate course curriculum. All MATLAB<sup>®</sup> files found in the book are available for download from the publisher's Web site. MATLAB<sup>®</sup> is a registered trademark of The MathWorks, Inc. For product information please contact

The MathWorks, Inc. 3 Apple Drive Natick, MA 01760-2098 USA Tel: 508-647-7000 Fax: 508-647-7001 E-mail: info@mathworks.com Web: www.mathworks.com

> Kris Iniewski, Coquitlam, BC, Canada

### About the Editor

**Krzysztof (Kris) Iniewski** is manager of research and development at Redlen Technologies Inc., a start-up company in Vancouver, Canada. Redlen's revolutionary production process for advanced semiconductor materials enables a new generation of more accurate, all-digital, radiation-based imaging solutions. Kris is also an executive director of CMOS Emerging Technologies (www.cmoset.com), a series of high-tech events covering communications, microsystems, optoelectronics, and sensors.

During his career Dr. Iniewski has held numerous faculty and management positions at the University of Toronto, the University of Alberta, SFU, and PMC-Sierra Inc. He has published over 100 research papers in international journals and conferences, and he holds 18 international patents granted in the USA, Canada, France, Germany, and Japan. He is a frequently invited speaker and has consulted for multiple organizations internationally. He has written and edited several books for Wiley & Sons, CRC Press, McGraw Hill, Artech House, and Springer.

His personal goal is to contribute to sustainability through innovative engineering solutions. He can be reached at kris.iniewski@gmail.com.

## List of Contributors

Anne-Johan Annema National Institute for Subatomic Physics (Nikhef) Amsterdam, the Netherlands

**Jean-Luc Autran** Université de Provence Marseille, France

**Gregory Avenier** STMicroelectronics Crolles, France

**Marco Bellini** ABB Zürich, Switzerland

**Bharat L. Bhuva** Vanderbilt University Nashville, Tennessee

Michael Caffrey Los Alamos National Laboratory Los Alamos, New Mexico

Lucio Carrara ESPROS Photonics Baar, Switzerland

**James Carroll** Brigham Young University Provo, Utah

**Gianluigi Casse** University of Liverpool Liverpool, UK

Andrea Cester Università degli Studi di Padova Padova, Italy Alain Chantre STMicroelectronics Crolles, France

**Edoardo Charbon** TU Delft Delft, the Netherlands

**Peng Cheng** Georgia Institute of Technology Atlanta, Georgia

**Pascal Chevalier** STMicroelectronics Crolles, France

**Lawrence T. Clark** Arizona State University Phoenix, Arizona

John D. Cressler Georgia Institute of Technology Atlanta, Georgia

**Ryan M. Diestelhorst** Georgia Institute of Technology Atlanta, Georgia

**Daniel M. Fleetwood** Vanderbilt University Nashville, Tennessee

**Gilles Gasiot** STMicroelectronics Crolles, France

**Cosimo Gerardi** Numonyx Catania, Italy

#### List of Contributors

**Derrick Gibelyou** Brigham Young University Provo, Utah

Paul Graham Los Alamos National Laboratory Los Alamos, New Mexico

Vladimir Gromov National Institute for Subatomic Physics (Nikhef) Amsterdam, the Netherlands

William Timothy Holman Vanderbilt University Nashville, Tennessee

William Howes Brigham Young University Provo, Utah

**Jonathan Johnson** Brigham Young University Provo, Utah

Jim Krone Los Alamos National Laboratory Los Alamos, New Mexico

Salvatore Lombardo CNR - IMM Catania, Italy

Kevin Lundgreen Brigham Young University Provo, Utah

**Juan Antonio Maestro** Nebrija Universidad Madrid, Spain

**Paul W. Marshall** NASA Washington, DC Lloyd W. Massengill Vanderbilt University Nashville, Tennessee

**Daniel McMurtrey** Brigham Young University Provo, Utah

Keith S. Morgan Los Alamos National Laboratory Los Alamos, New Mexico

**Daniela Munteanu** Université de Provence Marseille, France

**Balaji Narasimham** Broadcom Corporation Irvine, California

**Cristiano Niclass** EPFL Lausanne, Switzerland

Patrick Ostler Brigham Young University Provo, Utah

**Stanley D. Phillips** Georgia Institute of Technology Atlanta, Georgia

**Rosario Portoghese** Numonyx Catania, Italy

Brian Pratt Brigham Young University Provo, Utah

Heather Quinn Los Alamos National Laboratory Los Alamos, New Mexico

xiv

**Philippe Roche** STMicroelectronics Crolles, France

**Sébastien Sauze** Université de Provence Marseille, France

Ronald D. Schrimpf Vanderbilt University Nashville, Tennessee

**Noémy Scheidegger** Oerlikon Space Zurich, Switzerland

**Herbert Shea** EPFL Lausanne, Switzerland

**Robert L. Shuler, Jr.** NASA Johnson Space Center Houston, Texas

Marek Turowski CFD Research Corporation Huntsville, Alabama **Pedro Reviriego Vasallo** Nebrija Universidad Madrid, Spain

Massimo Violante Politecnico di Torino Torino, Italy

Michael Wirthlin Brigham Young University Provo, Utah

Arthur F. Witulski Vanderbilt University Nashville, Tennessee

Nicola Wrachien Università degli Studi di Padova Padova, Italy

Xing J. Zhou IBM Semiconductor Research and Development Center Hopewell Junction, New York

### Devices

# 1 Radiation Damage in Silicon

Gianluigi Casse

#### CONTENTS

| 1.1  | Introd | uction                                                  | 3  |

|------|--------|---------------------------------------------------------|----|

|      | 1.1.1  | Surface Damage                                          | 3  |

|      | 1.1.2  | Bulk Damage                                             |    |

| 1.2  | Annea  | aling of $I_{\rm R}$ and $N_{eff}$                      | 6  |

|      | 1.2.1  | Impurities in Silicon                                   |    |

|      | 1.2.2  |                                                         |    |

| 1.3  | Asses  | sing the Radiation Hardness of Silicon Detectors        | 11 |

|      | 1.3.1  | Silicon Detectors and High-Energy Physics Experiments:  |    |

|      |        | A Success Story                                         |    |

|      | 1.3.2  |                                                         |    |

|      | 1.3.3  | Radiation Tolerance of n-Side Readout Sensors           | 14 |

|      | 1.3.4  | Effect of Varying the Detector Thickness                | 18 |

|      | 1.3.5  | Reverse Current in Heavily Irradiated Thin and Standard |    |

|      |        | Silicon Sensors                                         | 20 |

|      | 1.3.6  | Radiation Tolerance of Different Single Crystal Silicon |    |

|      |        | 1.3.6.1 MCz Silicon                                     |    |

|      |        | 1.3.6.2 Epitaxial Silicon                               |    |

| 1.4  | Annea  | aling Effects                                           |    |

| 1.5  |        | usions: The ATLAS Example Case                          |    |

| Refe |        |                                                         |    |

#### 1.1 INTRODUCTION

The operations of silicon detectors are progressively degraded by radiation, ultimately leading to their failure. The radiation damage mechanism in the sensors can be divided in two classes: surface and bulk damage.

#### 1.1.1 SURFACE DAMAGE

The passage of ionizing radiation causes the build-up of trapped positive charge in the dielectric layer (usually  $SiO_2$ ) that covers the silicon detectors. The ionized e-h pairs either recombine or move in the oxide electric field: the electrons toward the  $SiO_2$ -Si interface and the holes toward the metallic contact. The higher mobile electrons escaped from the recombination are injected into the silicon bulk in a typical time of  $\approx 100$  ps. The less mobile holes can be trapped at the SiO<sub>2</sub>-Si interface. This trapping results in an increase of the oxide positive space charge with degradation of its quality. This charge build-up saturates at a value close to  $2 \times 10^{12}$  cm<sup>-3</sup> after a dose of about 100 kRad [1]. In addition to the trapped charge, the ionizing radiation also produces new energy levels in the band gap at the SiO<sub>2</sub>-Si interface [2]. These levels can be occupied by electrons or holes, depending on the position of the Fermi level at the interface, and the corresponding charge can be added or subtracted to the oxide charge. The effects of radiation on the oxide and the silicon surface depend on the specific detector design. The most relevant aspect for the operations of modern sensors is the formation of a conductive layer of electrons attracted to the interface by the positive oxide charge. This aspect will be briefly discussed later when presenting p-side readout segmented detectors.

#### 1.1.2 BULK DAMAGE

The radiation impinging onto the silicon crystal can cause point-like defects (a single silicon atom displaced from its lattice position) or *cluster* defects (a high concentration of damaged crystal in a volume with radius between 10 nm and 200 nm [3]), depending on the particle energy and type. It is known that protons produce more point-like and less cluster defects than neutrons, due to the different nature of the scattering with the crystal caused by the electromagnetic interaction. Also, the same particles with different energies produce different damage to the silicon crystal. The radiation-induced defects can be electrically neutral or active: in the second case they can act as generation-recombination or trapping centers of the charge carriers. In particular, they cause considerable changes in parameters relevant to the operation of silicon sensors, like the full depletion voltage ( $V_{FD}$ ), reverse current ( $I_R$ ), and the signal height (S).

To compare the effects of the various particles to the silicon lattice structure, the radiation damage is scaled using the *nonionizing energy loss* (NIEL) [4]. This quantity evaluates the energy deposited in the crystal by interactions that cannot be described by the reversible process of ionization. This scaling allows the macroscopic electrical properties of the silicon devices to be compared and is performed by folding the energy spectra of the particles of a given radiation field with the appropriate NIEL factor to express the fluence in terms of a reference monochromatic particle. The common reference particles are 1 MeV neutrons that have therefore a NIEL normalization factor k = 1. The NIEL normalized fluence is called the 1 MeV neutron equivalent ( $n_{eq}$ ). The radiation-induced changes in the reverse current have been found to scale well with the calculated NIEL normalization factors. As an example, the changes of the reverse current of identical silicon detectors irradiated with 24 GeV/c protons and 1 MeV neutrons match very well if the proton fluence is multiplied by k = 0.62.

After irradiation, the defects can interact with other mobile impurities in silicon (e.g., hydrogen, carbon or oxygen, interstitial silicon) and form permanent complexes with a possibly different electrical nature from the original ones. This *annealing* process is a function of time and temperature and changes again the electrical properties of the detectors.

The studies carried out with simple pad diodes have allowed the parameterization of the changes of the full depletion voltage and the reverse current as a function of irradiation and time after irradiation. Extensive literature is available on this subject; for a summary, see, for example, [5].

The  $V_{FD}$  is proportional to the effective space charge density ( $N_{eff}$ ):

$$V_{FD} = \frac{ew^2 |N_{eff}|}{2\varepsilon_0 \varepsilon_{Si}}$$

(1.1)

The changes of  $N_{eff}$  as a function of fluence are described by the following equation:

$$N_{eff}(\phi) = N_D e^{-c\phi} - N_A e^{-d\phi} + (\beta_D - \beta_A)\phi$$

(1.2)

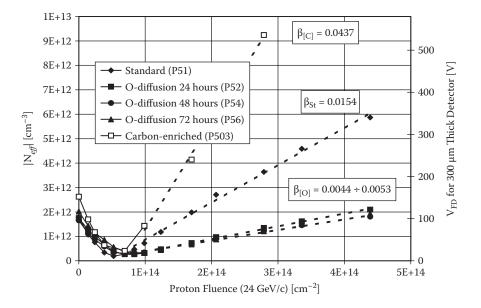

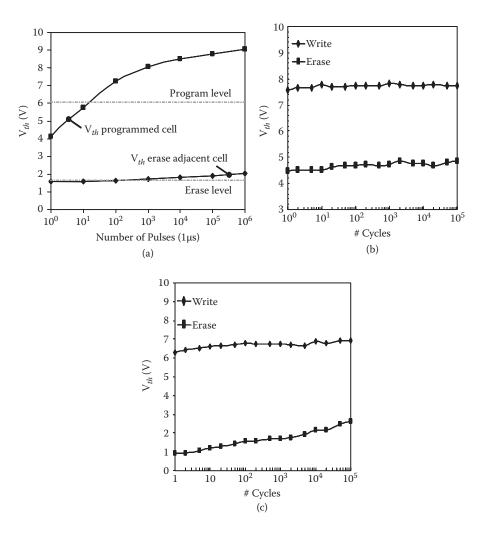

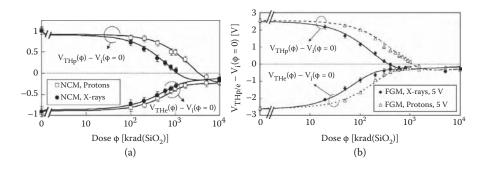

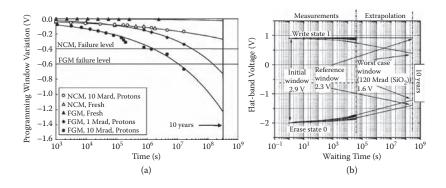

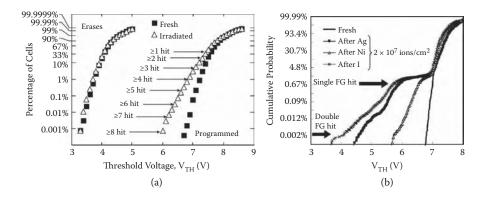

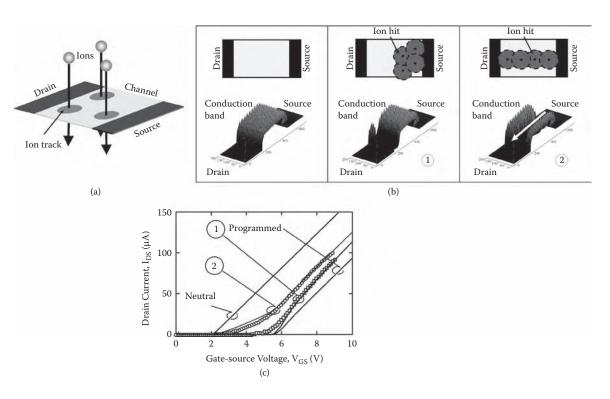

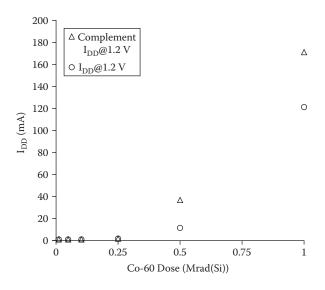

where  $N_{\rm D}$  is the initial donor concentration,  $N_{\rm A}$  is the initial acceptor concentration, c and d are removal constants, and  $\beta_A$  and  $\beta_D$  are the parameters accounting for the introduction of acceptor- or donor-like defects. The first two terms describe the exponential removal of the initial doping. In n-type silicon (p-type) the initial acceptor (donor) concentration  $N_{\rm A}$  ( $N_{\rm D}$ ) can be neglected. The second factor of Equation (1.2) describes the linear changes of  $N_{eff}$  with the radiation fluence. In fact, the radiation introduces defects acting as both types of doping, but the acceptor-like defects appear to be dominant, at least in high-resistivity detector-grade float-zone (FZ) silicon. The factor  $(\beta_D - \beta_A)$  is in general negative and can be replaced with an effective introduction of acceptor defects  $-\beta_{Aeff}$ . In this case, the initial (positive) doping concentration of n-type silicon decreases exponentially until conductivity-type inversion [6] to effective *p*-type and then becomes more negative linearly with fluence (Figure 1.1), at least up to the maximum doses where direct measurements have been performed (a few times 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup>). No space charge inversion has been measured with *p*-type bulk devices. Although this is true for the majority of the silicon crystal types studied, exceptions (depending on the impinging particle type) will be described as follows.

The reverse current  $I_{R}$  is proportional to the detector volume V and increases linearly with fluence:

$$\Delta I_R(\phi) = I_R(\phi, T) - I_R(\phi = 0, T) = \alpha_{T,t} \phi V$$

(1.3)

The *damage factor*  $\alpha_{T,t}$  depends on temperature and time after irradiation (annealing). The current of irradiated sensors depends exponentially on temperature and is described by the following expression:

$$I_R \propto T^2 \exp\left(-\frac{E_A}{k_B(T+273.2)}\right) \tag{1.4}$$

where the *activation energy*  $E_A$  is 1.12 eV. In practice, the reverse current decreases by a factor of ~2 by reducing the temperature by 9°C.

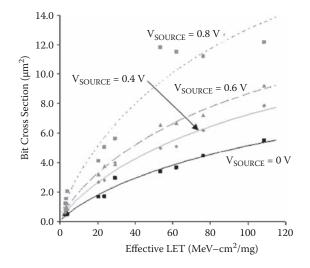

**FIGURE 1.1** Absolute value of  $N_{eff}$  ( $V_{FD}$ ) as a function of the proton fluence for standard, oxygen enriched and carbon enriched silicon. It is visible the initial exponential decay followed by the linear increase of the absolute value of the effective space charge, being in fact negative after type inversion. It is evident the advantage of oxygen enrichment and the opposite effect of carbon on the changes of these parameters [5]. (G. Lindstrom et al., "Radiation hard silicon detectors developments by the RD48 (ROSE) Collaboration," *Nucl. Instrum. Meth.* Vol. 466, Issue 2, July 1, 2001, pp. 308–326. With permission from Elsevier.)

#### 1.2 ANNEALING OF $I_{\rm R}$ AND $N_{\rm eff}$

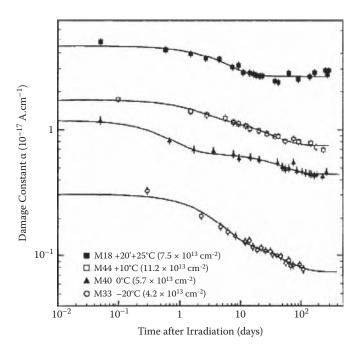

Both the full depletion voltage and the reverse current change with time after irradiation (*annealing*) [5,7–9]. The current decreases with a series of time constants,  $\tau_i$ , and can be parameterized as follows:

$$\Delta I_{Vol}(t,\Phi) = \Delta I_{Vol}(0,\Phi) \sum_{i} a_{i} \exp\left(-\frac{t}{\tau_{i}}\right), \quad \sum_{i} a_{i} \equiv 1$$

(1.5)

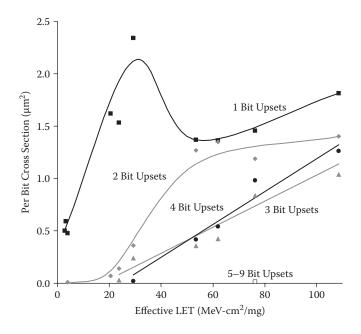

where the parameters'  $a_i$ 's weigh the various contributions to the reverse current with different annealing times. Different parameterizations exist (see, e.g., [5,8]), but they also introduce some arbitrary factor to reproduce the annealing of the current. Figure 1.2 shows an example of fits to the annealing of the reverse current after different levels of irradiation using Equation (1.5).

The annealing rate can be slowed down (accelerated) by lowering (increasing) the temperature. In fact, the time constants are an exponential function of the temperature through the following Arrhenius relationship [5,7]:

**FIGURE 1.2** Dependence of the reverse current damage factor on the time after irradiation at the indicated temperatures [9]. (F. Lemeilleur, S. J. Bates, A. Chilingarov, C. Furetta, M. Glaser, E. H. M., et al., "Study of characteristics of silicon detectors irradiated with 24GeV/c protons between -20°C and +20°C," *Nucl. Instrum. Meth.* Volume 360, Issues 1–2, June 1, 1995, pp.438–444. With permission from Elsevier.)

$$\frac{1}{\tau_i} = k_{0,i} \exp\left(-\frac{E_A}{k_B T_A}\right) \tag{1.6}$$

where  $E_A$  is the silicon energy gap. Due to the strong dependence of the current on temperature and annealing, when giving a value for the constant  $\alpha_{T,t}$  in Equation (1.3), it is necessary to specify these quantities. The value for  $\alpha_{T,t}$ , given in literature after an annealing time of 80 minutes at 60°C and at the reference temperature  $T_{REF} = 20^{\circ}$ C corresponds to  $3.99 \times 10^{-17}$  A cm<sup>-1</sup>.

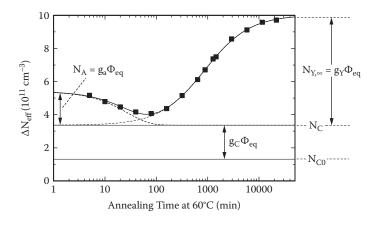

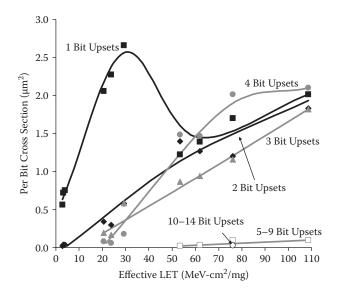

The dependence of  $N_{\rm eff}$  ( $V_{\rm FD}$ ) on the time after irradiation is shown in Figure 1.3 in the case of an inverted n-type detector.  $N_{\rm eff}$  is found to decrease during 80 minutes at 60°C (or about 30 days at  $T_{\rm REF}$ ). After this *beneficial short-term* annealing,  $N_{\rm eff}$  starts to increase again over many years at  $T_{\rm REF}$  up to an apparent saturation. This second phase of the  $N_{\rm eff}$  dependence on the time after irradiation is called *reverse annealing*. The first-phase (short-term) annealing is described by

$$N_{ST} = g_{ST} \exp\left(-\frac{t}{\tau_{ST}(T)}\right) \phi \tag{1.7}$$

**FIGURE 1.3** Evolution of N<sub>eff</sub> with time after irradiation for a conductivity type inverted n-type silicon detector. The various factors of the parameterisation are visualized. The minimum of this curve occurs at about 80 minutes at 60°C, corresponding to about 30 days at 20°C (the acceleration factor being about 540) [5]. (G. Lindstrom et al., "Radiation hard silicon detectors developments by the RD48 (ROSE) Collaboration," *Nucl. Instrum. Meth.* Vol. 466, Issue 2, July 1, 2001, pp. 308–326. With permission from Elsevier.)

with the usual Arrhenius dependence of the inverse of the short-term annealing rate  $\tau_{sT}$ :

$$\frac{1}{\tau_{ST}} = k_{ST} \exp\left(-\frac{E_{ST}}{k_B T_{ST}}\right)$$

with  $k_{\text{ST}} = (2.4 \pm 1) \times 10^{13} \text{ s}^{-1}$  and  $E_{\text{ST}} = 1.09 \pm 0.03 \text{ eV}$ .

The reverse annealing data (for t > 10 days) are well fitted by the form [5,8]

$$N_{Y}(\phi, t, T) = N_{C0}(\phi) + N_{Y\infty}(\phi) \left[ 1 - \frac{1}{\left(1 + \frac{t}{\tau_{LT}}\right)} \right]$$

(1.8)

where  $N_{C0}(\phi)$  is called the stable damage component,  $N_{Y_{\infty}}(\phi)$  is the saturation value at the end of the process, and  $t_{LT}$  is the reverse annealing rate constant.  $N_{C0}(\phi)$  defines the minimum value of  $V_{FD}$  after the short-term annealing and exhibits a certain variability for different materials. The amplitude of the reverse annealing can be expressed as a function of the fluence as

$$N_{Y\infty}(\phi) = g_Y \phi \tag{1.9}$$

with  $g_{\rm Y} = 5.16 \pm 0.09 \times 10^{-2} \, {\rm cm}^{-1}$ .

The dependence of the  $\tau_{LT}$  on temperature is again of the type

$$\frac{1}{\tau_{LT}} = k_{LT} \exp\left(-\frac{E_{LT}}{k_B T}\right)$$

(1.10)

with  $k_{LT} \cong 1.5 \times 10^{15} \text{ s}^{-1}$  and  $E_{LT} = 1.33 \pm 0.03 \text{ eV}$ .

The parametric functions shown here for the changes of  $N_{\text{eff}}$  and  $I_{\text{R}}$  have been determined experimentally by  $V_{\text{FD}}$  and  $I_{\text{R}}$  measurements of silicon diodes and not derived from fundamental kinetics of the defects and semiconductor generation-recombination statistics. The microscopic explanation for the annealing behavior is still not satisfactory, and the correlation between the identified radiation-induced defects and the annealing of the leakage current is not available.

#### **1.2.1** IMPURITIES IN SILICON

Two possible approaches to the radiation hardening of the silicon sensors are the engineering of the impurity content of the silicon substrate and the optimization of the geometry of the devices. The first approach has been extensively studied, especially by the dedicated CERN-RD48 research and development (R&D) project [10]. It has been shown [11] that the variation of the content of carbon and oxygen in the silicon crystal can have an effect on the degradation of some of the electrical properties with irradiation. In particular, a relatively high concentration of oxygen can reduce the degradation rate of  $N_{\rm eff}$  ( $V_{\rm FD}$ ) as a function of charged hadron fluence. Figure 1.1 shows a comparison of the changes of  $N_{\rm eff}$  as a function of 24 GeV/c proton fluence for standard and carbon- and oxygen-enriched n-type FZ silicon sensors. A reduction of the  $\beta_{Aeff}$  (with a value of 0.0044 cm<sup>-1</sup> if measured as a function of 24 GeV/c proton, or 0.007 cm<sup>-1</sup> for 1 MeV neutron equivalent fluence) is clearly seen in oxygen-enriched (to  $[O] \sim 2 \times 10^{17} \text{ cm}^{-3}$ ) wafers with respect to the standard  $(\beta_{Aeff} = 0.0154 \text{ cm}^{-1} \text{ with proton corresponding to } 0.025 \text{ cm}^{-1} \text{ with } 1 \text{ MeV } n_{eq} \text{ for a } 1000 \text{ cm}^{-1} \text{ with } 1 \text{ MeV } n_{eq} \text{ for a } 1000 \text{ cm}^{-1} \text{ with } 1000 \text{ cm}^{-1} \text{ c$  $[O] < 1 \times 10^{16} \text{ cm}^{-3}$ ) and carbon-enriched ones ( $\beta_{Aeff} = 0.0437 \text{ cm}^{-1}$  with protons or 0.07 cm<sup>-1</sup> with  $n_{eq}$ ). Unlike this result after proton irradiation, no significant effects have been measured with oxygen-enriched silicon sensors after neutron irradiation [5,11]. Also, no effect on changing the degradation rate of the reverse current (both after charged hadron or neutron irradiations) has been measured with any type of impurity-enriched silicon sensor with respect to the standard high-purity detectorgrade FZ silicon (Figure 1.2). Although these electrical parameters are important for defining the properties of irradiated silicon, they don't give any direct indication of the expected performances of the detectors.

The evolution of  $V_{\rm FD}$  has often been used as a qualifying parameter, because in nonirradiated detectors the capacitance versus voltage characteristic saturates at the same value of the charge collection. The ability of biasing the detector at voltages above  $V_{\rm FD}$  was considered a criterion for assessing the functionality of the device. It can be extrapolated from Figure 1.1 that  $V_{\rm FD}$  exceeds 1,000 V (for a 300 µm detector) above a fluence of about  $2 \times 10^{15} \, n_{eq} \, cm^{-2}$  in the more favorable case (oxygenated silicon irradiated with proton). If  $V_{\rm FD}$  was the qualifying parameter it is evident that

silicon detectors could hardly be used after this fluence due to the practical limitation to provide bias voltages  $\geq$  1,000 V in any large detector system.

#### 1.2.2 CHARGE TRAPPING AND CHARGE COLLECTION

The radiation-induced defects also contribute to the reduction of the signal height by means of trapping of the signal charge carrier for a time exceeding the charge collection time. The density of the defects increases linearly with fluence; therefore, the trapping is assumed to have the same trend. In fact, it can be described by a parameter called the trapping time,  $\tau_{tR}$ , which is inversely proportional to the concentration of trapping centers and therefore to the fluence:

$$\frac{1}{\tau_{tr}(\phi)} = \frac{1}{\tau_{tr}(\phi=0)} + \beta_{tr}\phi$$

(1.11)

The trapping for nonirradiated detectors is order of magnitudes higher than  $\tau_{tr}$  even after moderate doses of hadron irradiation, and the first term of Equation (1.11) can be neglected. The measured values of  $\beta_{tR}$  range from 0.41 × 10<sup>-6</sup> cm<sup>2</sup> s<sup>-1</sup> and 0.62 × 10<sup>-6</sup> cm<sup>2</sup> s<sup>-1</sup> for electrons and holes, respectively [12].

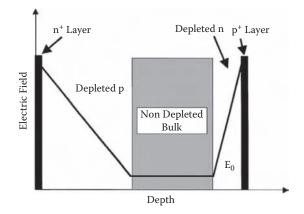

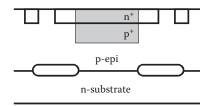

The signal is influenced to a different extent depending on the readout geometry of the irradiated detectors. The silicon detectors are made by high-density doping implants (n<sup>+</sup> and p<sup>+</sup>) on low doped bulk to form the diode junction and the ohmic contact. P-in-n sensors have a p<sup>+</sup> diode side and n-in-p sensors an n<sup>+</sup> diode side. As shown in Figure 1.4, due to the introduction of defects acting as acceptor doping with the radiation damage, the silicon bulk is effectively *p*-type after a few  $10^{13}$  cm<sup>-2</sup> of hadron irradiation, irrespective of the original space charge sign. The electric field of inverted n-type silicon detectors is stronger under the implanted n<sup>+</sup> contact [13], like in *p*-type bulk detectors, although a narrow region with high field is present also on

**FIGURE 1.4** Schematics of the electric field profile of an irradiated and inverted n-type (or a *p*-type) silicon detector. The stronger electric field has shifted from the original junction side (under the  $n^+$  implant) to the former ohmic side (n+ implant).

the p<sup>+</sup> contact (this effect is usually called double junction)[13,14]. Due to the profile of the electric field, it is advantageous in terms of charge collection to segment and read-out the detectors from the n-side. In fact, the signal deficit caused by trapping of the charge carriers at radiation-induced defect centers can be described by the following equation:

$$N_{e,h}(t) = N_{e,h}(0) \exp\left(-\frac{t_c}{\tau_{tr,e,h}}\right)$$

(1.12)

where  $N_{\rm e,h}$  is the number of collected charges (electron or holes, respectively),  $N_{\rm e,h}(0)$  is the number of ionized electrons and holes,  $t_{\rm c}$  is the collection time, and  $\tau_{\rm tr,e,h}$  is the electron and hole effective trapping time.

From Equation (1.12) it is clear that a shorter  $t_c$  provides substantial advantages in terms of collected charge. If segmented n-type silicon devices are read out from the  $n^+$  side (n-in-n detectors), the signal will mainly be formed by the electron current and will benefit from a shorter  $t_c$ , with respect to the standard p-in-n, due to the faster electron collection (higher mobility carriers moving in the higher electric field with respect to holes) [15,16]. The n-side readout is, however, more readily achieved with *p*-type substrates (n-in-p), where no inversion takes place with irradiation and the main electric field is always located on the original n<sup>+</sup>-p junction side. A difference between n-in-n and n-in-p detectors is that in the first case double-sided processing is needed to implant edge protection structures on the back side (guard rings) with significant impact on the complexity and cost (up to 50% higher) of the processing with respect to *p*-type substrates that require only front-side guard ring implants [17]. This turns out to be a very important factor for experiments where a large coverage area is required, due to the cost reduction and easier handling of single-sided devices. The expected improvement of the charge collection properties and the simpler processing of the *p*-type substrate n-side readout sensors motivated the proposal of this type of devices as competitive radiation tolerant detectors [18,19].

#### 1.3 ASSESSING THE RADIATION HARDNESS OF SILICON DETECTORS

A possible definition of radiation tolerance is the maximum fluence at which the devices are fully functional. This definition is certainly setup and device dependent. A considerable difference is found between *pad diodes* and the more complex finely segmented detectors. These latter typically have one or both the electrodes segmented in individual diode structures with at least one dimension comparable to or smaller than the thickness of the sensor: microstrip detectors have the readout contact realized in the strip with a typical pitch size from under 40  $\mu$ m to a few hundred  $\mu$ m, and pixel sensors can be made in a 50  $\mu$ m × 50  $\mu$ m size or larger. The typical thickness of silicon detectors varies from 300  $\mu$ m to over 1,000  $\mu$ m. The segmented sensors are used in fast and precise tracking systems thanks to their speed and resolution. The degradation of their functionality implies quantities like the reduction of the signal size, the increase of the electronics noise, and the possible deterioration of the resolution. In the following we neglect the latter because it is a convolution of many effects, also involving the electronics readout.

The increase of the electronics noise is dependent on the performance of the readout electronics, the geometrical parameters of the detector (e.g., through the input capacitance of the individual channels), and the operating conditions (e.g., the temperature, determining the intensity of the reverse current and its contribution to the noise). All these parameters are known in the design phase of the detector system. The main parameter to be determined for predicting the functionality of the irradiated sensors is the reduction of the signal with fluence. A smaller signal yields a reduced efficiency. The concept of acceptable efficiency varies in different applications (e.g., 50%-80% in the case of gamma rays imaging in space experiments [20] to close to 100% in particle physics ones [21,22]). Besides, the efficiency after irradiation is very dependent on the applied bias voltage ( $V_{\rm B}$ ), and different systems can tolerate very diverse ranges of applicable  $V_{\rm B}$ 's: a limited range with low maximum bias voltage is acceptable for experiments in space, while voltages up to 1,000 V are possible in high-energy or nuclear physics accelerator experiments. In the following we discuss the radiation tolerance of finely segmented detectors designed for highenergy physics (HEP) as a representative example. This application is particularly demanding for it requires accurate position sensitivity and tracking efficiencies close to 100% for particles at the minimum ionization energy (mips). These particles yield a small signal (the ionized charge is about 79 electrons per micron of silicon crossed by a mip); its degradation as a function of fluence could lead to an early failure of the tracking system.

#### 1.3.1 SILICON DETECTORS AND HIGH-ENERGY PHYSICS EXPERIMENTS: A SUCCESS STORY

Since planar processing was developed around 1980 ([23]), finely segmented (pixel and microstrip) silicon detectors have been used to cover ever larger areas in highenergy physics experiments (see, e.g., [24] for a review). The reason for this success is their low mass, high speed, and resolution, which allow for fast three-dimensional (3-D) reconstruction of charged particle tracks in very high multiplicity collision events. All the more recent HEP experiments use mainly silicon sensors for tracking and vertexing. In particular, all four major experiments hosted by the Large Hadron Collider (LHC) [25] at the CERN accelerator complex in Geneva use an unprecedented number of silicon detectors [21,22,26,27]. The LHC is presently the frontier machine, with 14 TeV center of mass energy interactions of proton-proton bunches colliding at 40 MHz, for a design luminosity of 10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>. The radiation environment created by the multitude of relativistic particles emerging from the p-p collisions and the intense flux of neutrons (with average energy of about 1 MeV) backscattered from the calorimeter regions of the experiments are extremely challenging. The segmented silicon detectors (microstrip and pixel sensors) developed for this machine have been designed to survive 10 years worth of experiments, with a maximum final fluence of about  $2 \times 10^{15} n_{eq} \text{ cm}^{-2}$ . Their radiation tolerance requirements have stimulated a significant effort in radiation hardening of silicon detectors for well over the 10 years preceding their installation in 2007. Upgrading this machine (the Super-LHC, SLHC) presents a new, more severe challenge to a factor of 10 higher luminosity [28], with a similar increase in the expected radiation tolerance: the SLHC sensors will have to operate up to about  $2 \times 10^{16} n_{eq} \text{ cm}^{-2}$ .

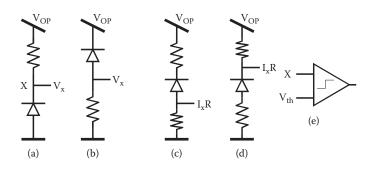

An efficient way of defining the radiation tolerance of the detectors for this application is the signal-over-noise (S/N) ratio. An S/N of 10 is considered a safe limit for high-efficiency (percentage of identified tracks) and high-purity (rejection of fake events) mip tracking in HEP experiments (where over 98% track hit efficiency and a few 10<sup>-5</sup> noise occupancy hits are required). To have an idea of the expected noise, the present electronics for microstrip detectors has typically

$$ENC = 400 + 45 \times C_{load} \tag{1.13}$$

where the equivalent noise charge (*ENC*) is expressed in electrons, and  $C_{\text{load}}$  is the input capacitance to the individual electronics channels in picofarads (pF). A typical value of  $C_{\text{load}}$  for 80 µm pitch silicon strips on a 300 µm thick silicon detector is about 0.7 pF/ cm. Another contribution to the *ENC*, which is to be added in quadrature to Equation (1.12), comes from the shot noise induced by the fluctuations of the reverse current:

$$ENC = \sqrt{12I_R t_{SH}} \tag{1.14}$$

with  $I_{\rm R}$  in nA and  $t_{\rm SH}$  in ns. The estimate of the shot noise contribution is performed by evaluating the reverse current at the operating temperature per electronics channel after the appropriate dose of irradiation. The missing ingredient to determine the functionality of the sensors is the degradation of the signal with fluence. This parameter is largely independent of the particular readout system; thus, its evaluation allows the prediction of the radiation tolerance of every silicon detector system. To give a specific example of radiation environment we can use the layout of the upgraded ATLAS experiment at the SLHC [29]. This detector has cylindrical geometry around the axis of the colliding proton beams and comprehends four layers of pixel detectors from 3.8 cm to 21 cm and five layers of microstrip detectors from 38 cm to 100 cm cm radii from the beam line. The most demanding radiation tolerance is for the pixel sensors, with the expected fluences ranging from  $2 \times 10^{16} n_{eq} \text{ cm}^{-2}$  (~1 Grad) to  $3 \times 10^{15} n_{eq} \text{ cm}^{-2}$  (150 Mrad) from the inner to the outer layer. The innermost microstrip sensors will receive a final fluence of  $1 \times 10^{15} n_{eq} \text{ cm}^{-2}$  (50 Mrad).

The evaluation of the signal as a function of the hadron fluence and the estimate of the noise on the basis of the known geometry and the measured reverse current after irradiation allow the determination of the achievable S/N ratio at the different radii at the end of the physics program of the experiment.

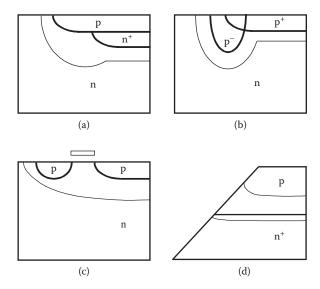

#### 1.3.2 RADIATION HARDENING OF SILICON DETECTORS

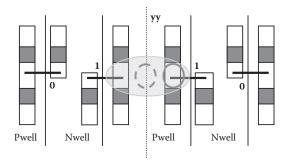

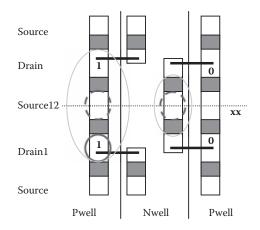

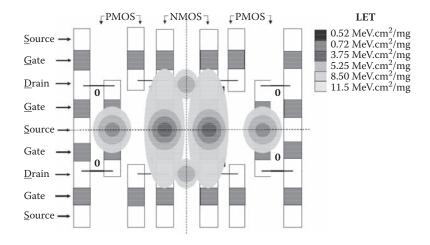

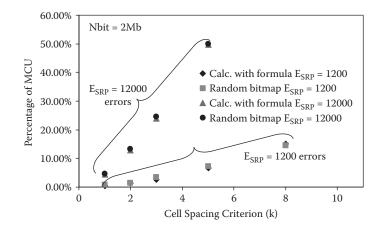

As previously mentioned, the radiation hardening of silicon sensors can be pursued by exploiting different geometry options and by engineering the silicon crystal bulk with impurities. Figure 1.1 showed some advantages offered by oxygen-enriched silicon after proton irradiation. Some possible enhancements of the charge collection of detectors made with silicon crystals other than the high-purity FZ (i.e., the standard for detector applications) are discussed in this section, but the more important results in terms of radiation hardening of silicon sensors were obtained by changing the geometry of the readout segmented electrodes. It has been previously discussed that the electron signal (n-side readout) allows for a shorter collection time with predicted benefits in terms of reduction of the charge trapping. Nonetheless, tracking planar silicon sensors have been traditionally produced by implanting p<sup>+</sup> segmented structures on n-type high-resistivity silicon. This is due to the simplicity of this technology, because no special care for isolating the implanted structures has to be taken, unlike with segmented n+ implants. A low-resistivity connection between n-implants is caused by an electron accumulation layer at the interface Si-SiO<sub>2</sub> created by the positively charged oxide. This positive charge increases with irradiation (until saturation), as briefly mentioned before. The electron layer can be interrupted, and the n-electrodes (strips, pixels) isolated, by means of dedicated structures: p-spray (a shallow homogeneous p-implantation over the whole wafer [30]); p-stop implants (photo-lithographically defined p-implants between the readout strips [31]); or a combination of the two methods [32].

Using one of these methods, n-side readout devices can be produced. The extra processing complication has actually a large payout in terms of performances after irradiation.

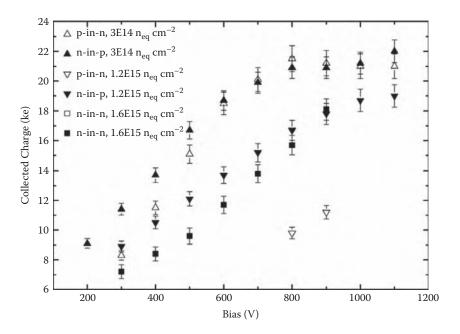

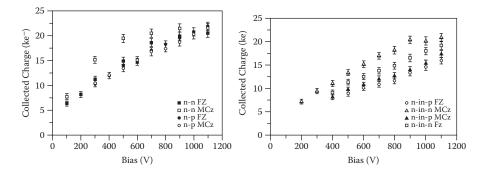

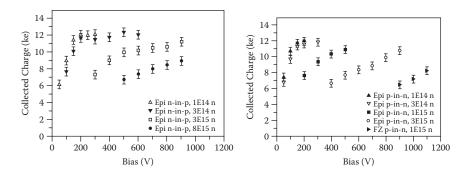

Figure 1.5 shows the comparison of the charge collected by n-in-n, n-in-p, and a p-in-n sensor after 3 and  $12 \times 10^{14}$  n<sub>eq</sub> cm<sup>-2</sup>. After the lower dose, comparable performances (although the n-side readout shows superior charge collection at low bias voltages) are measured, while after the higher fluence the p-side readout is considerably lower performing. The remarkable difference in signal between the two readout sides is measured despite a similar value of  $V_{\rm FD}$  after the same dose of irradiation. It is apparent that the effect of the n-side readout is not dependent (for radiation doses at which the *n*-type silicon is inverted) on the substrate, and n- and p-silicon substrates perform equally well with this type of readout. The use of *p*-type substrates is a simpler and cheaper processing for implementing the n-side readout. The extra complexity and cost involved in processing n-in-n single-sided sensors would be justified only by a substantial advantage in terms of radiation hardness, but no appreciable difference is measured between n-side readout sensors made with the two types of FZ substrates.

#### 1.3.3 RADIATION TOLERANCE OF N-SIDE READOUT SENSORS

Having proved that irradiated n-side readout sensors deliver a considerably superior signal than p-side readout ones, this paragraph aims to establish in absolute terms the signal degradation with fast hadron fluence with this type of detector made with high-resistivity FZ materials (both n and p conductivity type). The results reported here were obtained after irradiations with charged and neutral hadrons to investigate possible differences in the charge collected as a function of the bias voltage (CC(V)) due to the different nature of the damage. The fluences are all given in 1 MeV n<sub>eq</sub>

**FIGURE 1.5** Signal as a function of the bias voltage for n-in-n and n-in-p silicon microstrip sensors after 24GeV/c proton irradiation to 3 and  $12 \times 10^{14} n_{eq} \text{ cm}^{-2}$ . Also an n-in-n sensor irradiated to  $16 \times 10^{14} n_{eq} \text{ cm}^{-2}$  is shown. Taking into account the difference in the irradiation dose, the n-in-n and n-in-p detectors behave very similarly. The significantly smaller signal delivered by the p-in-n sensors is well noticeable.

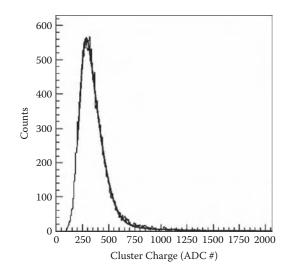

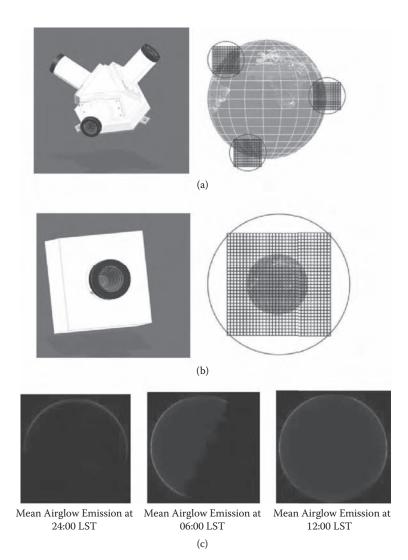

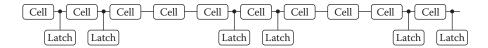

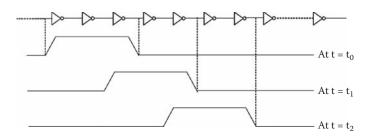

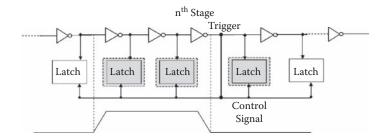

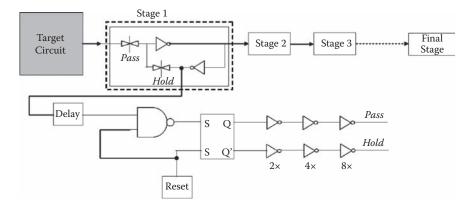

using the standard NIEL normalization. The detectors used for the measurements presented here are  $\sim 1 \times 1 \text{ cm}^2$ , 80 µm pitch silicon sensors (128 channels) coupled with 25 ns shaping time electronics, 40 MHz clock rate (SCT128 [33]). The measurements were performed at about  $-25^{\circ}$ C to control the reverse current. The minimum ionizing particle signal is mimicked by fast electrons from a <sup>90</sup>Sr, and the signal is expressed in number of collected electrons at the most probable value of the distribution of the charge ionized in silicon by a passing mip (Figure 1.6).

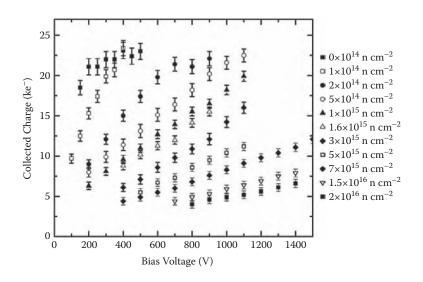

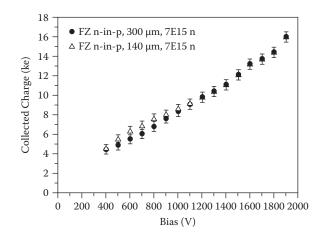

Figure 1.7 shows the CC(V) of n-in-p sensors after various reactor neutron [33,34] doses, up to  $2 \times 10^{16} n_{eq} \text{ cm}^{-2}$  (about 1 Grad). This dose is well in the range for qualifying the sensors to the most demanding radiation tolerance for the aforementioned high-energy physics application (SLHC). The signal degradation with fluence is clear. Nonetheless, approximately 5,000 e<sup>-</sup> are still collected at 1,000 V after the highest fluence.

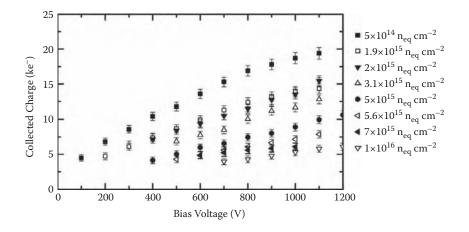

Figure 1.8 shows the CC(V) of n-in-p sensors after various 26 MeV and 24 GeV/c proton [34,35] doses, up to  $2.2 \times 10^{16} n_{eq} \text{ cm}^{-2}$ . A similar discussion as for the neutron irradiations also holds for these measurements. A charge of about 5,000 e<sup>-</sup> is collected here at 1,000 V after  $1.6 \times 10^{16} n_{eq} \text{ cm}^{-2}$  and about 4,000 e<sup>-</sup> after  $2.2 \times 10^{16} n_{eq} \text{ cm}^{-2}$ . It can be noted that after corresponding NIEL normalized fluences, the CC(V) of detectors irradiated with both energy protons are well comparable, indicating a similar damage from the relatively low energy and the relativistic protons.

**FIGURE 1.6** Charge distribution deposited by a minimum ionizing particle in silicon. The most probable value of this distribution corresponds to ~24000 electrons in 300 µm silicon.

**FIGURE 1.7** Degradation of the signal as a function of the bias voltage for n-in-p silicon microstrip sensors irradiated with neutrons to various doses up to  $2 \times 10^{16} \, n_{eq} \, cm^{-2}$ .

**FIGURE 1.8** Degradation of the signal as a function of the bias voltage for n-in-p silicon microstrip sensors irradiated with 26 MeV and 24GeV/c protons to various doses up to  $2.5 \times 10^{16} n_{eq} \text{ cm}^{-2}$ .

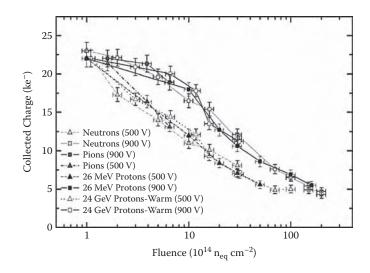

A summary of the degradation of the signal measured at 500 V and 900 V as a function of neutrons, and protons with different energies and 280 MeV pions [37] is shown in Figure 1.9. The decrease of the signal after the various types of irradiation shows a good degree of agreement within the experimental errors on the fluence and on the measured charged.

It is important to stress that the collected charge is well above the expectations derived by the measurement of the increase of the charge-trapping probability. Using the parameterization in [12], the expected charge collection distance after  $1 \times 10^{16}$

**FIGURE 1.9** Degradation of the signal of n-in-p silicon microstrip sensors at 500V and 900V as a function of the  $n_{eq}$  fluence of various energies protons, pions and neutrons.

$n_{eq}$  cm<sup>-2</sup> would be less than 30 µm, for less than 2,400e<sup>-</sup> maximum collected charge. The much bigger size of the signal at high doses indicates that some mechanism is enhancing the charge collection after heavy irradiation. Possible explanations are a nonlinear dependence of the charge trapping after high doses, a possible field-enhanced fast detrapping, or a controlled charge multiplication at high electric fields in irradiated devices [38].

#### **1.3.4 EFFECT OF VARYING THE DETECTOR THICKNESS**

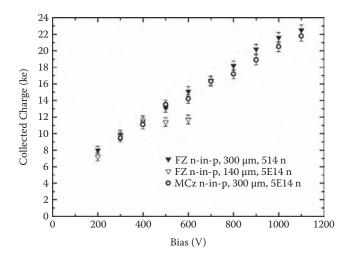

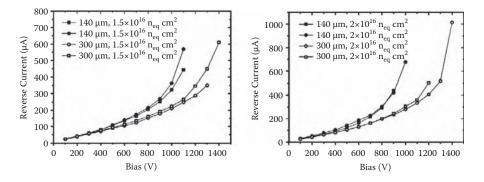

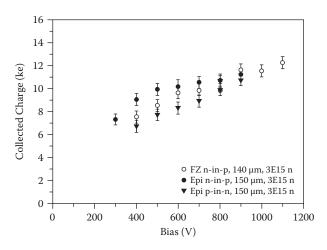

The signal generated by a mip crossing a silicon detector is proportional to the path length of the particle in the sensor, and the ionized charge is about 79 e/µm. This charge is entirely collected by a nonirradiated detector when the device is biased at or above full depletion voltage, thanks to the presence of a strong electric field in the entire volume of the sensor. After irradiation, two effects contribute to reduce the collected charge: (1) the charge carrier trapping at radiation-induced defect centers in the crystal; and (2) a lower electric field (for the same bias voltage) due to the increased effective space charge. In particular, after heavy hadron irradiation, a substantial electric field might occupy a volume smaller than the detector (on the junction side) even for very high applied voltages. In this situation the effective charge collection distance (CD), influenced by these two effects, is shorter than the detector thickness and progressively reduced by further irradiation. At high doses the CD defines the sensitive volume of the sensor. Thinner detectors could have an advantage with respect to the standard thickness (300 µm) when the CD is shorter than this value, due to a possible higher average electric field over the active volume of the irradiated sensor for the same applied voltage. To explore this possibility, the charge collection properties of standard (300 µm) and thinned (140 µm) n-in-p readout sensors have been studied after various doses of hadron irradiation up to  $2 \times 10^{16} n_{eq} \text{ cm}^{-2}$  [39,40]. Different behaviors of the thin and thick devices are reported at different fluences. At the lower doses investigated (up to  $3 \times 10^{15} n_{eq} \text{ cm}^{-2}$ ), all the devices collect a similar charge with increasing bias voltage, until the charge collected by the thinner devices saturates (see an example in Figure 1.10). It should be noticed that the saturation value is very close to the maximum preirradiation charge (12,000 e<sup>-</sup>), so to the entire ionization charge released by a mip. After  $7 \times 10^{15} n_{eq} \text{ cm}^{-2}$ , the thin device is slightly more efficient in collecting charge at corresponding bias voltages up to a maximum of 1,100 V (Figure 1.11). Above this voltage, the thick sensor delivers a higher signal (indicating a CD larger than 140  $\mu$ m), up to the maximum applicable voltage of 1,900 V. This remarkably high bias voltage can be applied only after the device has been irradiated (breakdown voltages of less than 500 V are usually measured for this type of nonirradiated device). The slight improvement exhibited by the thinner sensors in the lowest part of the CC(V) curve is confirmed after ever higher fluences.

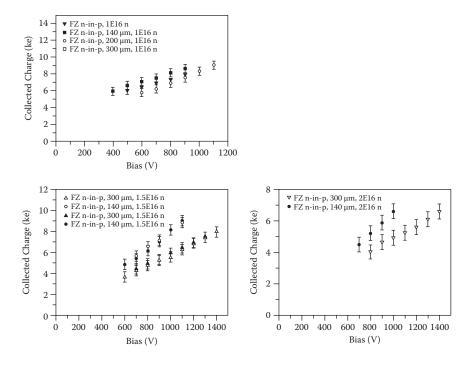

Figure 1.12 shows the CC(V) of 140  $\mu$ m and 300  $\mu$ m thick n-in-p sensors after extremely high doses: 1, 1.5, and 2 × 10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>. The data show a better charge collection at every applicable bias voltage (before thermal runaway) from the thin devices. A higher value ranging from about 10% after the lowest to over 25% after the two higher fluences is measured with the 140  $\mu$ m thick *p*-type sensors. The highest measured charge corresponds to a mip ionization distance of 110  $\mu$ m at 900 V after 1

**FIGURE 1.10** Collected charge as a function of the bias voltage for thin (140  $\mu$ m) and standard (300  $\mu$ m) n-in-p detectors irradiated to 5 × 10<sup>14</sup> n<sub>eq</sub> cm<sup>-2</sup>. The charge collected by the thin sensor saturates just under 12,000 electrons (the pre-irradiation value for this detector thickness).

**FIGURE 1.11** Collected charge as a function of the bias voltage for thin (140  $\mu$ m) and standard (300  $\mu$ m) n-in-p detectors irradiated to 7 × 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup> (left) and 1 × 10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup> (right).

**FIGURE 1.12** Collected charge as a function of the bias voltage for thin (140  $\mu$ m) and standard (300  $\mu$ m) n-in-p detectors irradiated to 1, 1.5 and 2 × 10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>.

× 10<sup>16</sup>  $n_{eq}$  cm<sup>-2</sup>, 110 µm at 1,100 V after 1.5 × 10<sup>16</sup>  $n_{eq}$  cm<sup>-2</sup>, and 75 µm at 900 V after 2 × 10<sup>16</sup>  $n_{eq}$  cm<sup>-2</sup>, if no trapping effects are taken into consideration. On the other hand, thin devices can tolerate a lower applied bias voltage than the thicker ones. In the case of the sensors irradiated to the two highest fluences the 300 µm sensors could be measured up to 1,400 V, while no more than 1,100 V could be applied to the thin ones.

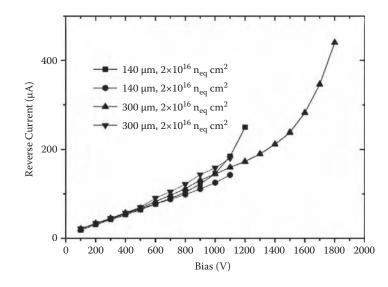

#### 1.3.5 REVERSE CURRENT IN HEAVILY IRRADIATED THIN AND STANDARD SILICON SENSORS

As said before, the reverse current of irradiated silicon detectors increases linearly with the irradiation fluence and is proportional to the volume of the silicon sensor. The increase of the reverse current is an important limiting factor to the operation of the irradiated sensors. As shown before, the charge collected by irradiated sensors keeps increasing as a function of the applied bias voltage. If an arbitrarily high voltage could be applied to heavily damaged devices, a significant amount of charge could be recovered and the lifetime of the detectors notably extended. Excluding possible practical limits of real detector systems (where routing voltages higher than 1,000 V could raise technical difficulties), the limitation to the maximum applicable voltage comes from the thermal runaway of the reverse current. In fact, it is experimentally verified that a destructive breakdown of the junction does not take place in irradiated devices, because it is preceded by the rapid increase of the reverse current

**FIGURE 1.13** Reverse current as a function of the bias voltage for 140 and 300  $\mu$ m thick silicon microstrip detectors irradiated to 7 × 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup>.

with time. The mechanism is due to the increased current drawn by a warmer detector. This excess current in turn generates heat, further increasing the reverse current. This thermal runaway takes place when the cooling is not capable of removing all the heat generated within the sensor. The failure to provide adequate bias for collecting the minimum signal due to the excess reverse current could be the first failure mode for irradiated sensors. The control of  $I_{\rm R}$  is therefore a very important parameter for detector systems under heavy radiation. The use of low temperatures to control the current is the first method to limit  $I_{\rm R}$ . On the other hand, the use of thin silicon could be envisaged to this purpose because  $I_R$  is proportional to the volume. This idea has been tested with 140 µm and 300 µm thick sensors [39], and the typical results are shown in Figure 1.13. Up to medium-high doses (aound  $7 \times 10^{15} n_{ea} \text{ cm}^{-2}$ ) the reverse current is essentially equal for both thicknesses of sensors up to the point that the sensitive volume of the thicker device becomes larger than the thin detector. But after the very high doses the differences between the current of the two thickness are somewhat unexpected (Figure 1.14). The current of the thin devices is always higher, and a thermal runaway occurs at 1,100 V, preventing stable operation of the devices. The thermal runaway also takes place for the thicker sensors, but at a higher value of the bias voltage, although at a similar value of the reverse current in both cases. It can be concluded that 140 µm thick devices have similar performances (or they display the same CC(V) and reverse currents) to standard thickness sensors at lower bias voltages (about 400 V lower) for hadron irradiation fluences above  $1 \times 10^{16} n_{ea} \text{ cm}^{-2}$ .

#### 1.3.6 RADIATION TOLERANCE OF DIFFERENT SINGLE CRYSTAL SILICON

As suggested already, the different content of some impurities (mainly oxygen and carbon) in the silicon crystal can affect the degradation rate of some of the electrical

**FIGURE 1.14** Reverse current as a function of the bias voltage for 140 and 300  $\mu$ m thick silicon microstrip detectors irradiated to 1.5 and 2 × 10<sup>16</sup> n<sub>eq</sub> cm<sup>-2</sup>.

properties of silicon diodes. In terms of performances of tracking detectors, it is important to investigate if the advantages are seen also with charge collection measurements with segmented sensors.

#### 1.3.6.1 MCz Silicon

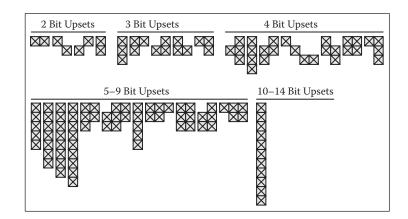

The high-purity FZ method yields high-resistivity wafers with very low concentrations of O ( $\sim 10^{16}$  cm<sup>-3</sup>) and other impurities. A much higher O concentration is found in wafers produced with the Cz method (~10<sup>18</sup> cm<sup>-3</sup>). This type of single crystal is usually employed by the microelectronics industry, but its very low resistivity makes it unsuitable for particle detectors where low  $V_{\rm FD}$  (therefore high resistivity) values are required. A novel production technique that combines the classical Cz method with a magnetic field (MCz) to reduce the concentration of impurities, allowing higher resistivity in the single-crystal ingot, has been made available by industry in recent years [41]. The O concentration in MCz silicon is about 4 to  $5 \times 10^{17}$  cm<sup>-3</sup>. n- and *p*-type single-crystal ingots with relatively high resistivity (1–2 k $\Omega$  cm) have been produced with this method and proposed as a possibly radiation harder substrate for silicon detectors (see, e.g., [42]). The degradation rate of the  $V_{\rm FD}$  for this type of sensor irradiated with neutrons is sensibly lower than for standard and oxygen-enriched FZ silicon [43]. Also, CC(V) measurements confirm the enhanced radiation tolerance of this material after neutron irradiations. Figure 1.15 shows the comparison of the CC(V) of n-side readout detectors made on n- and p-type substrates grown with both FZ and MCz methods and irradiated with neutrons to 5 and  $10 \times 10^{14} n_{eg} \text{ cm}^{-2}$ [44]. The nMCz detector exhibits the fastest rising signal with bias voltage, resulting therefore in the most performance after these doses. It can be noticed that the maximum collected charge is essentially the same for all materials. This indicates that the charge trapping is material independent and the improvement found with the nMCz crystal is due to a lower degradation of  $V_{\rm FD}$ .

In high-energy physics applications, and, namely, in the SLHC environment, the radiation field is mainly composed of backscattered neutrons and charged particles emerging from the interactions. Their ratio will depend on the radial distance from the beam axis, with the charged hadron dominating at low radii and the 1 MeV

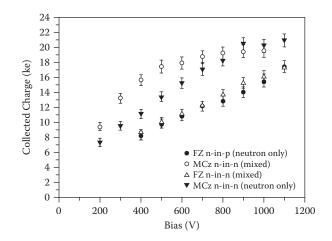

**FIGURE 1.15** Collected charge as a function of bias with the four type of detectors used for this study after 1 and  $5 \times 10^{14}$  neutrons cm<sup>-2</sup>. All detectors are configured to read-out on segmented n-implant electrodes.

neutrons being the main cause of damage at outer ones. The radius at which the two components are equal is about 25 cm. It has been found that these two types of radiation introduce a different ratio of donor (n-type) or acceptor (p-type) defects on different silicon crystals. In the case of FZ sensors, both radiations introduce predominantly p-type defects. In the case of n-MCz, the neutrons introduce mainly p-type defects, while charged particles mainly n-type defects. This effect was measured by capacitance-voltage measurements on diodes irradiated with one or the other type of radiation [45]. This particular feature of the n-MCz silicon could be advantageous for detectors exposed to radiation fields composed of a comparable mix of neutrons and charged hadrons because the n- and p-type radiation-induced defects can partially compensate. To test this effect, n-in-p FZ and n-in-n MCz detectors have been irradiated with neutrons only and n-in-n FZ and n-in-n MCz detectors with an equal mix  $(5 \times 10^{14} n_{eq} \text{ cm}^{-2})$  of neutrons and 26 MeV/c protons for a total dose of  $1 \times 10^{15} n_{eq} \text{ cm}^{-2}$  for every sensor. Figure 1.16 shows the CC(V) measurements of these devices and confirms the compensation effect. The two FZ detectors exhibit almost identical CC(V) characteristics after both the neutron and mixed irradiation, while the n-MCz shows a faster rise of the CC(V) in the case of mixed irradiation when compared with an identical detector irradiated with neutrons only [46]. This feature of the n-MCz material can efficiently extend the lifetime of detectors in applications where silicon tracker sensors have to operate after very high doses of a mixed irradiation field.

#### 1.3.6.2 Epitaxial Silicon

Epitaxial grown silicon layers (Epi) on low-resistivity Cz substrates are commonly used in the complementary metal-oxide semiconductor (CMOS) electronics industry. The typical thickness of the Epi layer is < 10  $\mu$ m. The use of thicker layers of this material for processing enhanced radiation hard detectors was proposed in [47]. Encouraging results have been obtained in terms of reduced degradation of the full depletion voltage with fluence. The main disadvantage with this material is the cost and the difficulty of growing thick (for epitaxial growth standards) layers of singlecrystal, relatively high-resistivity (> 500  $\Omega$  cm) silicon. The control of the growth-

**FIGURE 1.16** CC(V) of n-in-n and n-in-p FZ and n-in-n MCz detectors irradiated with neutron only or with an equal dose of neutrons and 26 MeV protons to the same total dose of  $1 \times 10^{15}$  n<sub>eq</sub> cm<sup>-2</sup>. The compensation effect of acceptor and donor-like defects introduced by the two different types of radiation in the nMCz substrate is visible in the faster rise of the CC(V) in the case of mixed irradiation. (G. Casse, A. Affolder, P.P. Allport, "Studies on Charge Collection Efficiencies for Planar Silicon Detectors after Doses up to 1016 Neq/cm2 and the Effect of Varying Substrate Thickness," 2008 Nuclear Science Symposium, 19–25 October 2008 Dresden, Germany, http://www.nss-mic.org/2008/Program/ListProgram. asp?session=N54, to be published in *IEEE Trans. Nucl. Sci.*)

processing parameters becomes problematic, and the yield and reproducibility of the Epi wafers can be affected. Nevertheless, *p*- and *n*-type Epi silicon layers up to 150 µm, 500  $\Omega$  cm have been obtained on 4-inch Cz wafers. Some of these wafers have been processed to produce 1 × 1 cm<sup>2</sup>, 80 µm pitch microstrip sensors. A few devices were selected and irradiated to various doses of reactor neutrons [40]. In general, high reverse currents were measured with the Epi irradiated detectors, but it was possible to select a few samples to measure the charge collection properties of n-in-p detectors up to 8 × 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup> and p-in-n detectors up to 3 × 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup> (Figure 1.17).

The Epi sensors are able to collect almost the same charge as before irradiation up to  $3 \times 10^{15}$  n<sub>eq</sub> cm<sup>-2</sup>, though at increasing bias voltages. The degradation of the p-in-n devices is faster than the n-in-p, as expected. The p-in-n Epi have, however, a much reduced degradation rate with respect to p-in-n FZ sensors. Also, the n-in-p Epi exhibit a reduced degradation rate with respect to FZ detectors of comparable thickness (Figure 1.18).

The epitaxial grown substrates display better relative performances after irradiation than any other silicon substrate. Despite these good results, the cost and the reproducibility of the performances with thick Epi layers make these substrates unlikely to be competitive for high-energy physics applications where the sensitive volume is required to be over 100  $\mu$ m thick. Also, epitaxial detectors are expected to demonstrate enhanced performance if operated in a mixed (charged and neutral particles) irradiation field due to the opposite sign of the effective space charge induced

**FIGURE 1.17** Collected charge as a function of the bias voltage for Epi (150µm) n-in-p detectors irradiated to various doses up to  $8 \times 10^{15} n_{eq} \text{ cm}^{-2}$  and p-in-n detectors to  $3 \times 10^{15} n_{eq} \text{ cm}^{-2}$  [40]. (With permission from G. Casse, A. Affolder, P. P. Allport, "Charge collection Efficiency Measurements for Segmented Silicon Detectors Irradiated," *IEEE Trans. Nucl. Sci.*, vol. 55, Issue 2, 2008, pp1695–1699.

**FIGURE 1.18** Comparison of n-in-p Epi and FZ sensors with similar active thickness after  $3 \times 10^{15} n_{eq} \text{ cm}^{-2}$ .

by the two types of radiation [45], as for the nMCz substrate, although CC(V) measurements of this effect are not available.

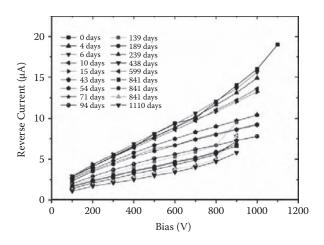

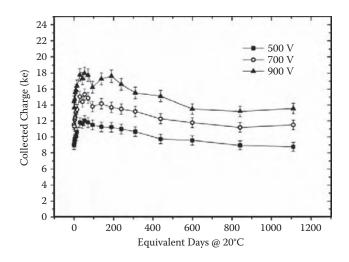

# 1.4 ANNEALING EFFECTS

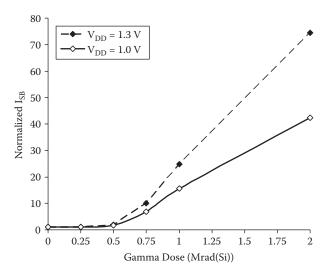

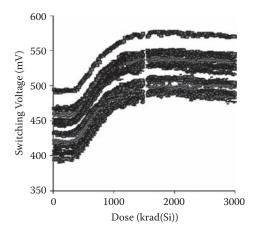

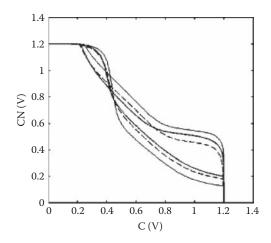

After Equation (1.5), the reverse current of the irradiated silicon sensors could be reduced by annealing. The annealing is a strong function of temperature and can be effectively used to suppress or accelerate this effect. Figure 1.19 shows the measured changes of the reverse current as a function of the annealing time. The data are shown in terms of equivalent annealing time at 20°C, but the measurements have been taken after accelerated annealing steps at 60°C (acceleration factor about 540) and 80°C (acceleration factor about 7,400) [49,50].

**FIGURE 1.19** Changes of the reverse current as a function of the bias voltage, measured at  $-25^{\circ}$ C, of a silicon detector irradiated to  $1 \times 10^{15}$  n<sub>eq</sub> cm<sup>-2</sup> with different annealing time after irradiation. The sensor was annealed at 60°C but the time are rescaled to equivalent time at T<sub>REF</sub>.

As shown, a substantial reduction of the current is achieved (between 30% to 40% at high voltage after  $\sim$ 50 days at 20°C). In certain applications (e.g., highenergy physics experiments) the reduction of the current by means of annealing is not exploited because of the reverse annealing of the  $V_{\rm FD}$ . This has always been considered detrimental to the sensor operations because of the increase of  $V_{\rm FD}$  after a short-term decrease for about 30 days at  $T_{\text{REF}}$  (Figure 1.3). It was assumed that this increase would entail a corresponding decrease of the charge collected at a given voltage below  $V_{\rm FD}$ . But studying the charge collected at a given voltage as a function of the accelerated (at 60°C and 80°C) annealing time with n-side readout detectors, a different picture emerged. The collected charge at any given bias voltage increased to reach a maximum after about 40 days (20°C equivalent). Up to a 30% increase in the collected charge has been verified (Figure 1.20). The signal stays > 20% higher than the starting value for about 300 days and returns to its initial value after about 1,100 days. The results of these measurements have changed the way the reverse annealing is regarded in high-energy physics experiments. In fact, the annealing can be used to achieve two important goals: (1) recovering some fraction of the signal height; and (2) reducing the reverse current.

# 1.5 CONCLUSIONS: THE ATLAS EXAMPLE CASE

As a conclusion, we can anticipate the S/N performance for the ATLAS upgrade at the SLHC. The pitch of the innermost strips is 75  $\mu$ m for a length of 2.5 cm. The pixels are 50  $\mu$ m wide and 250  $\mu$ m long. As mentioned before, the target doses are  $1 \times 10^{15} n_{eq} \text{ cm}^{-2}$  (innermost strips),  $3 \times 10^{15} n_{eq} \text{ cm}^{-2}$  (outermost pixels), and  $2 \times 10^{16} n_{eq} \text{ cm}^{-2}$  (innermost pixels). Assuming an operation temperature of  $-25^{\circ}$ C, the noises in the three cases, calculated using Equations (1.12) and (1.13) for the microstrip sensors with the measured currents (before annealing) after the corresponding

**FIGURE 1.20** Changes of the signal collected by a silicon detector irradiated to  $1 \times 10^{15} n_{eq}$  cm<sup>-2</sup> with time after irradiation. The sensor was annealed at 60°C but the time axis has been rescaled to equivalent time at  $T_{REF}$

radiation doses, and the present estimate for the pixel sensor noise (with a different parameterization from Equation (1.12)) are ~650 ENC, < 300 ENC, and < 400 ENC, respectively. Looking at the signal after the corresponding radiation doses, the S/N expected for the innermost microstrip layer is about 17 at 500 V and 25 at 900 V. For the two pixel layers, the S/N is about 23 at 500 V and 30 at 900 V for the outer pixels and 11.2 and 12.7 for the inner ones. As already stated, these values are for unannealed detectors and can be considered worst immediately after irradiation. A significant improvement is expected if a controlled annealing at 20°C (corresponding to between 100 to 300 days during the lifetime of the experiment). Nonetheless, the S/N values demonstrate that these detectors are in principle capable of operating fully efficiently after the highest doses of the most demanding application in high-energy physics.

## REFERENCES

- 1. H.E. Boesch et al., IEEE Trans. Nucl. Sci. vol. NS-3, no. 6, 1981, pp. 1191–1197.

- H.E. Boesch and T.L. Taylor, "Charge and interface state generation in field oxides," *IEEE Trans. Nucl. Sci.* vol. NS-31, no. 6, 1984, p. 1273.

- 3. K. Gill et al., J. Appl. Phys. vol. 82, no. 1, July 1997.

- 4. G.P. Summers et al., IEEE Trans. Nucl. Sci. vol. 34, 1987, p. 1134.

- G. Lindstrom et al., "Radiation hard silicon detectors developments by the RD48 (ROSE) Collaboration," *Nucl. Instrum. Meth.* vol. A466, 2001, pp. 308–326.

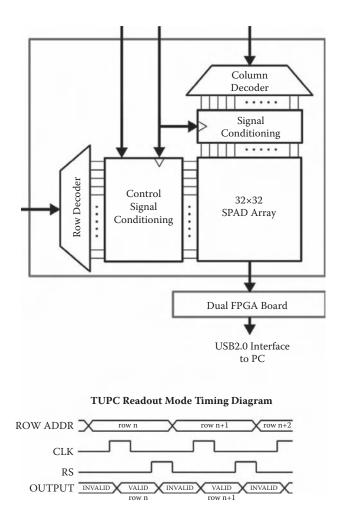

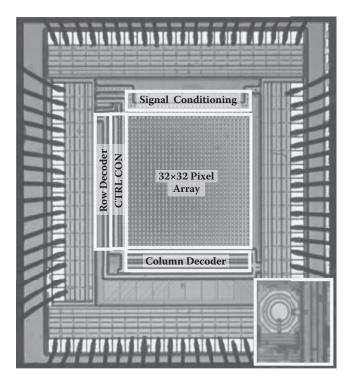

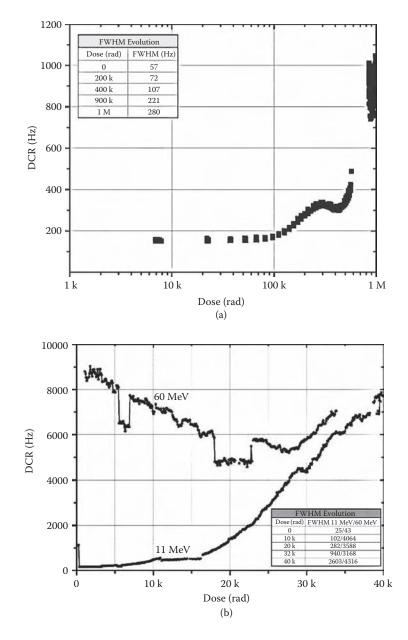

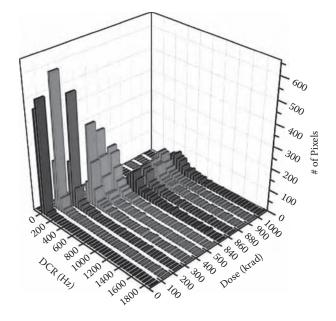

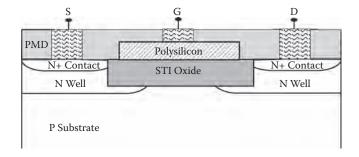

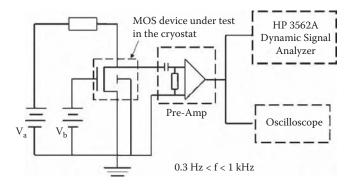

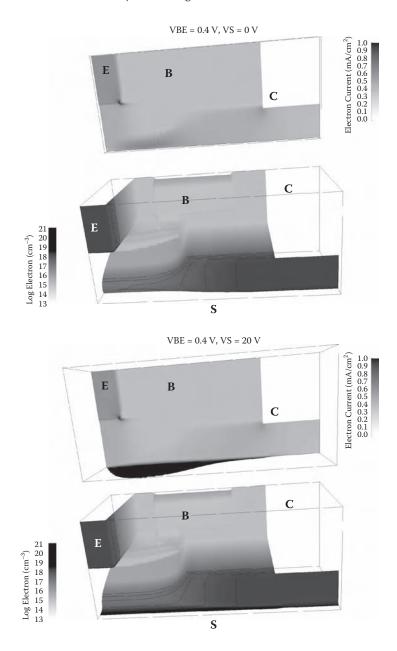

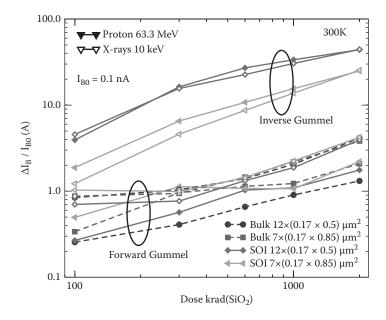

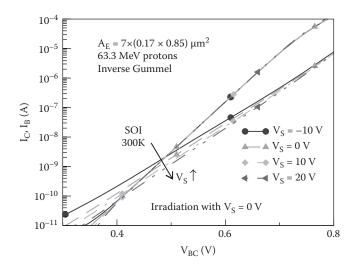

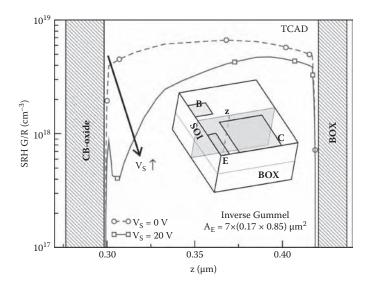

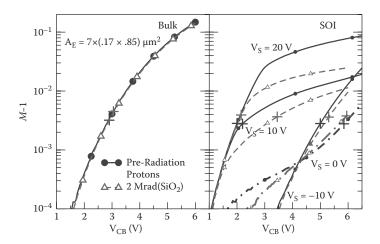

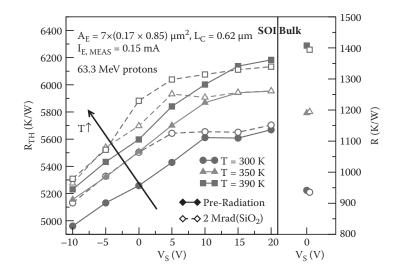

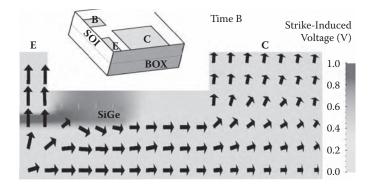

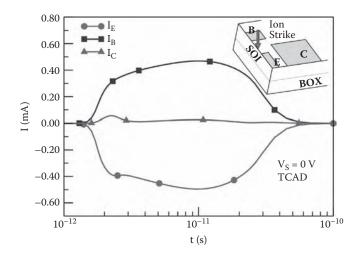

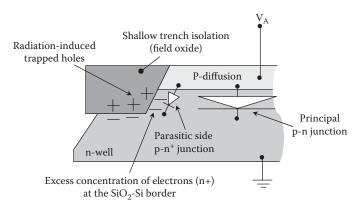

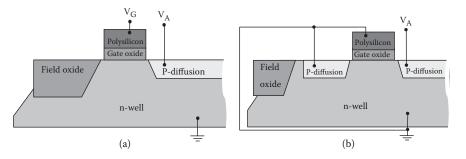

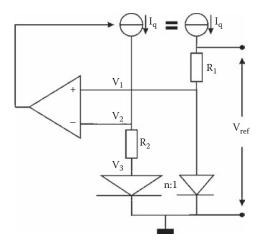

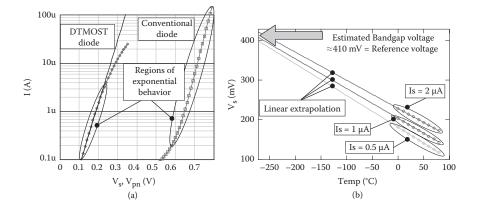

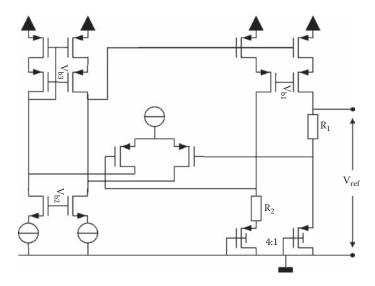

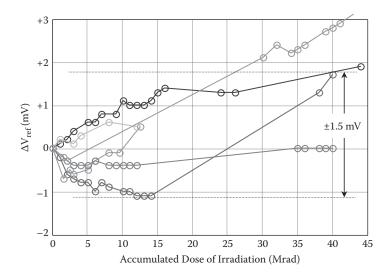

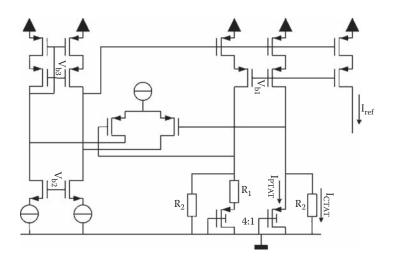

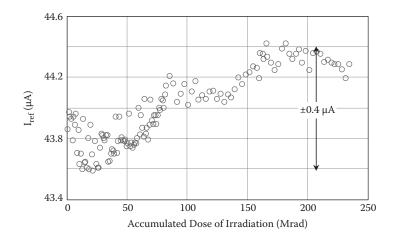

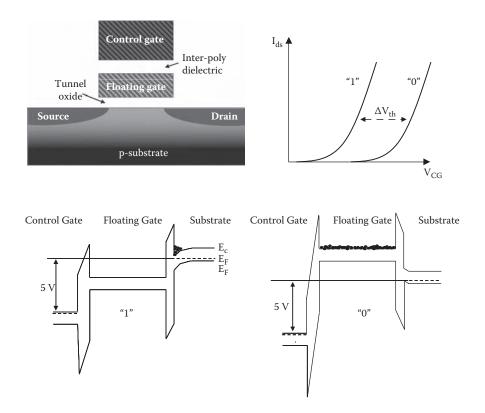

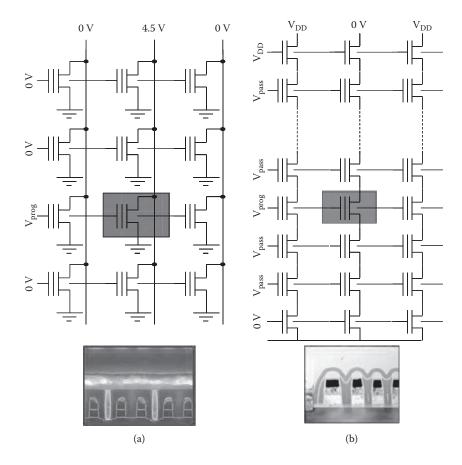

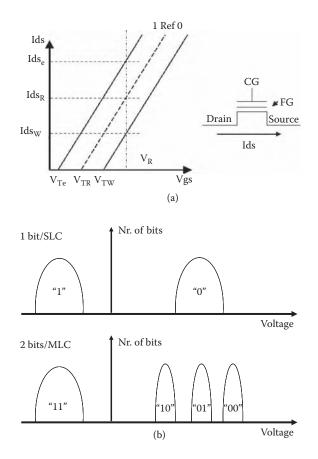

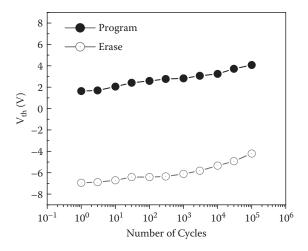

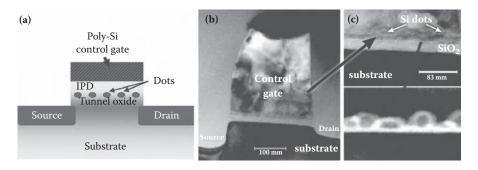

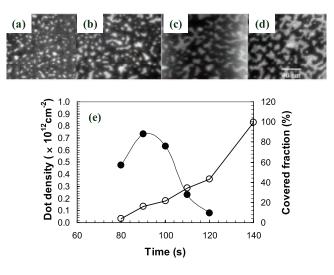

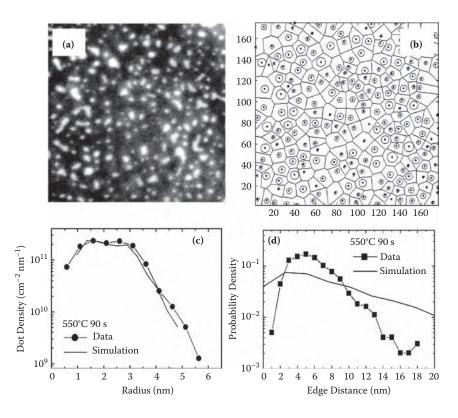

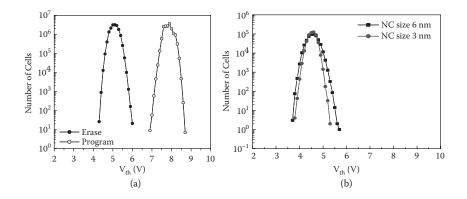

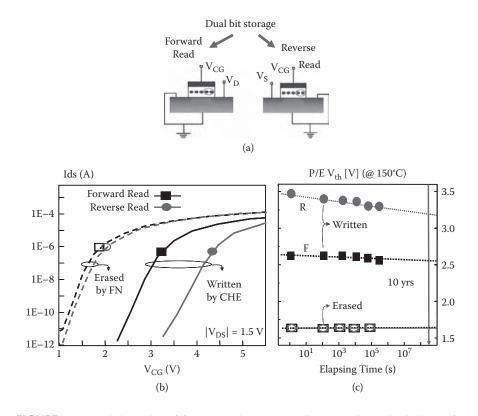

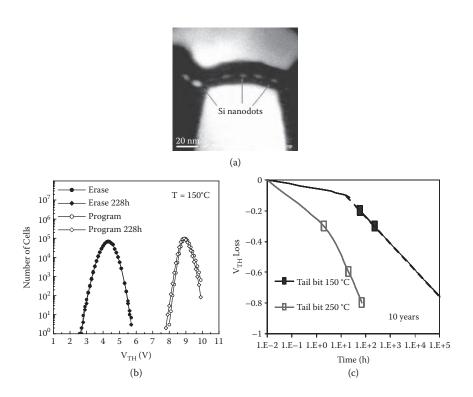

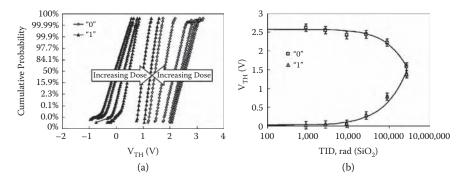

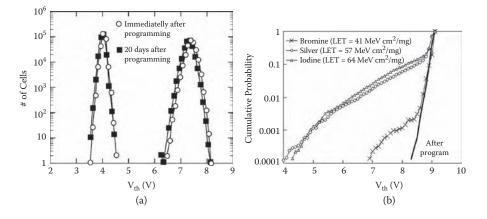

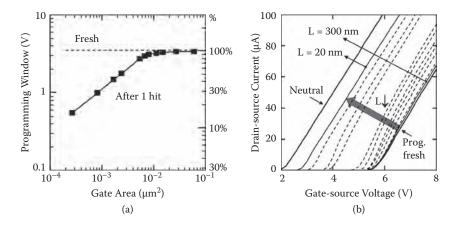

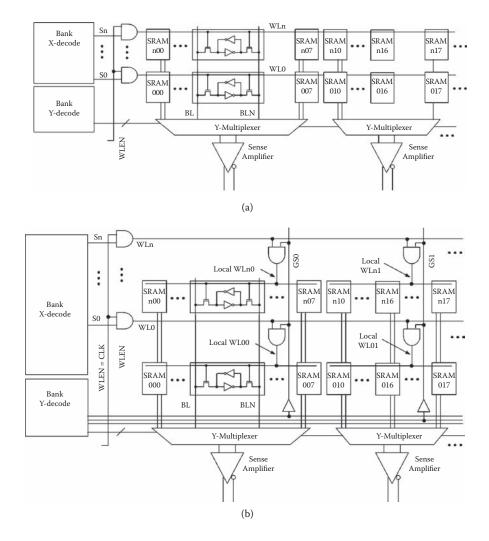

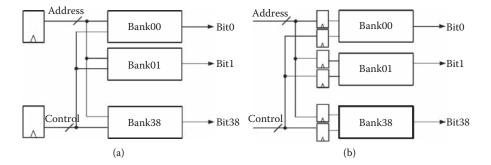

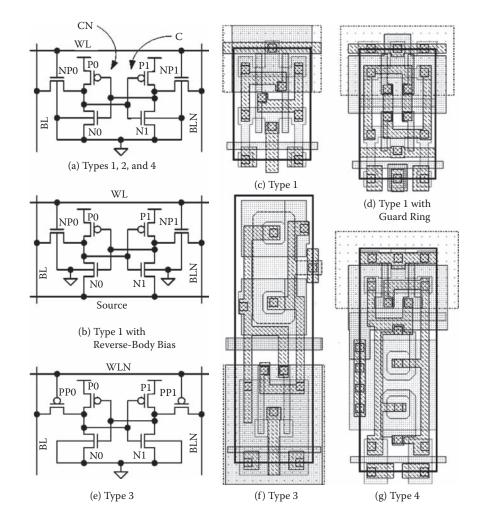

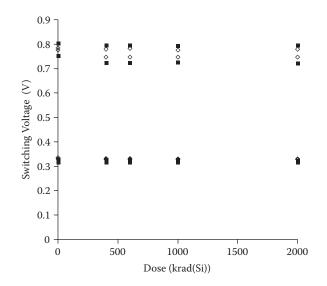

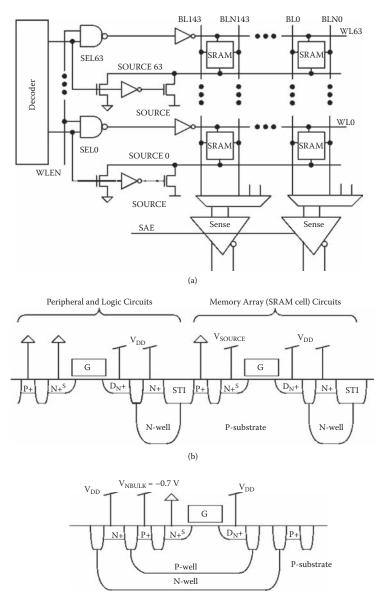

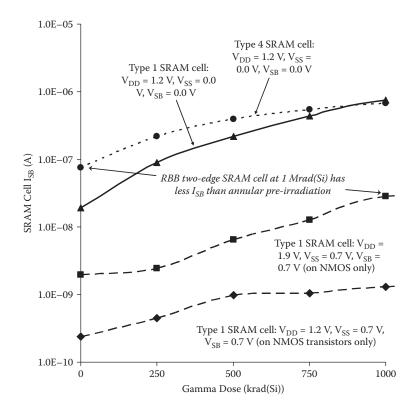

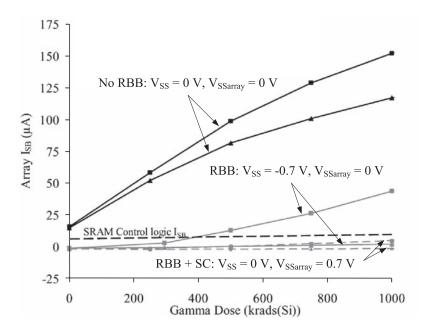

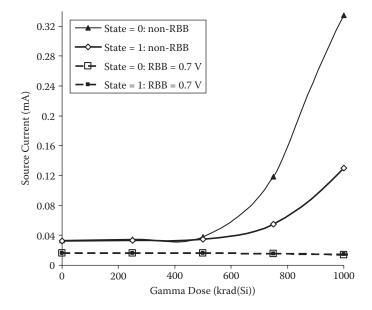

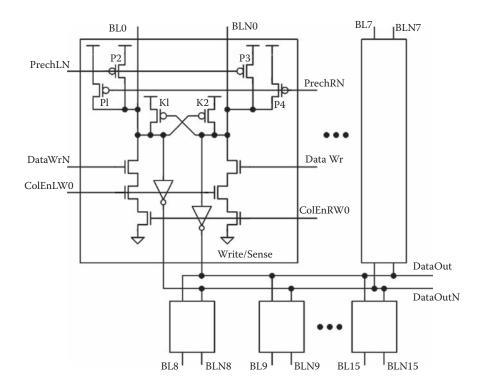

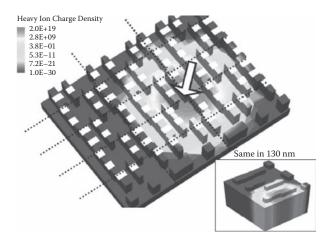

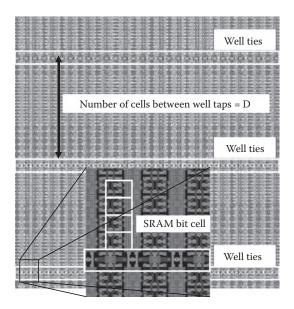

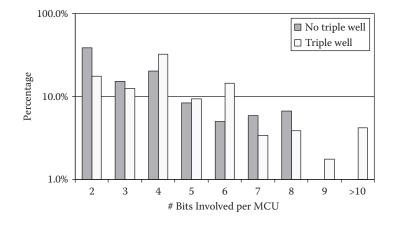

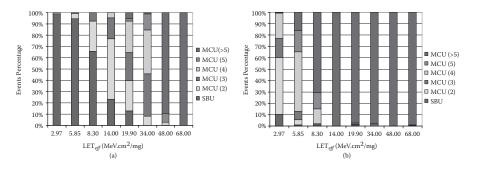

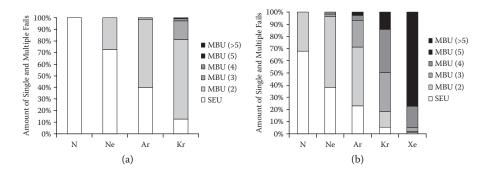

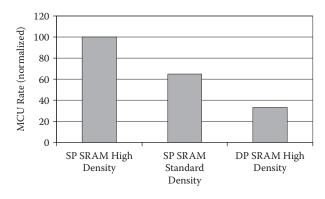

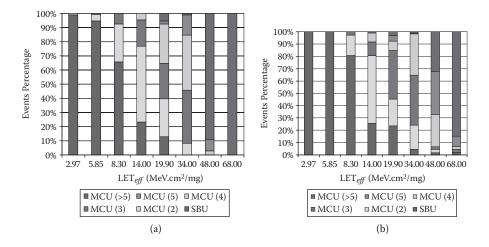

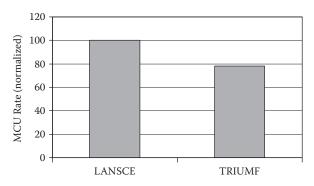

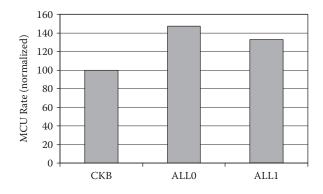

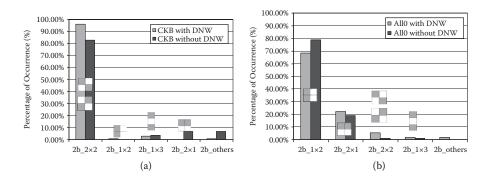

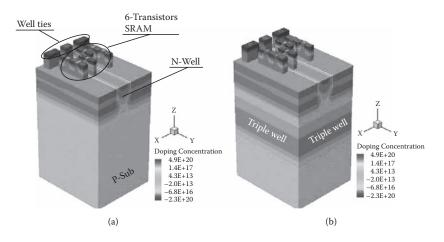

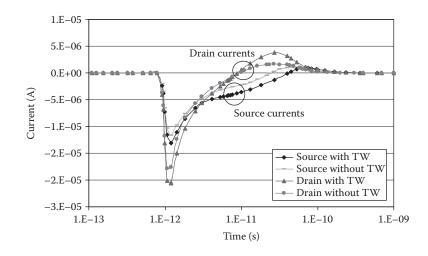

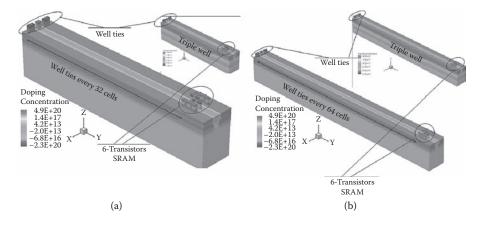

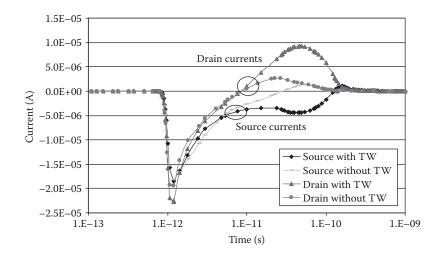

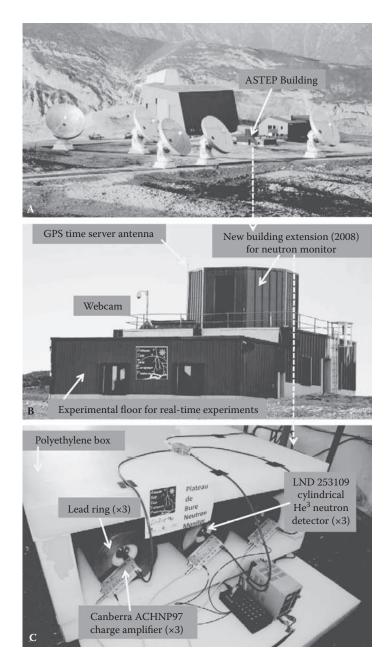

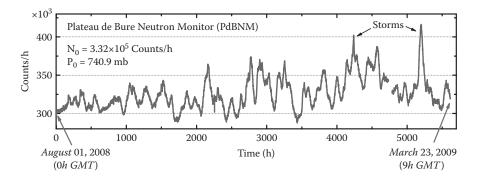

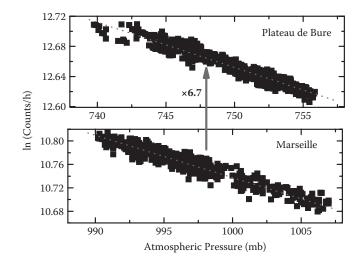

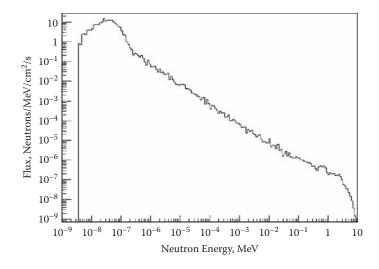

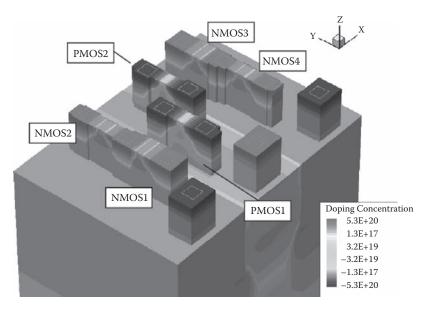

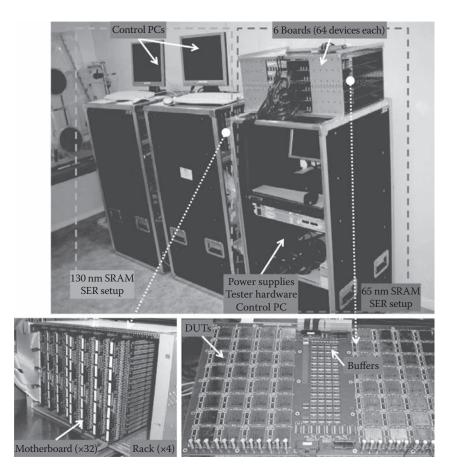

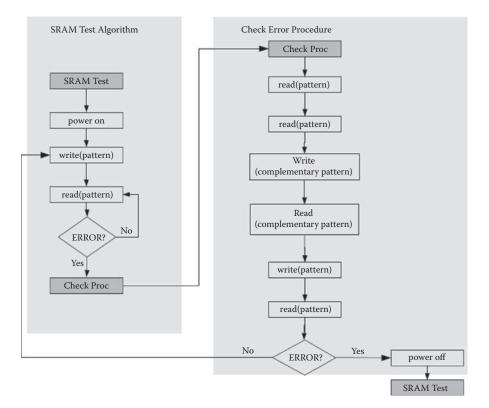

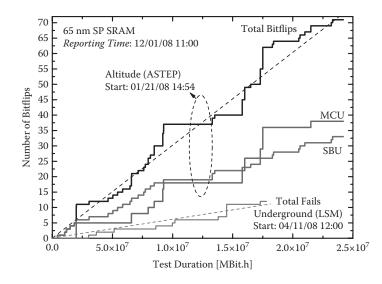

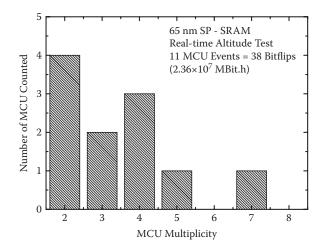

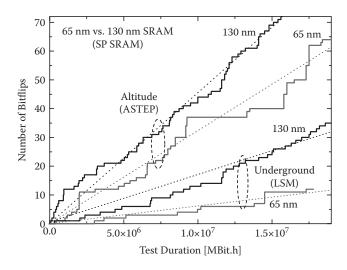

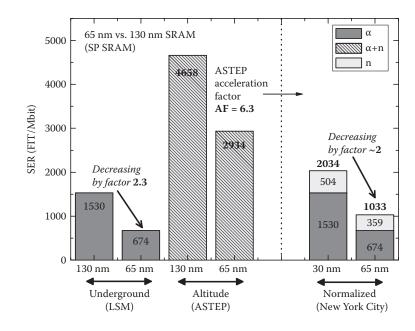

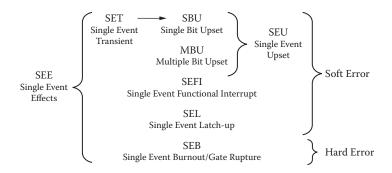

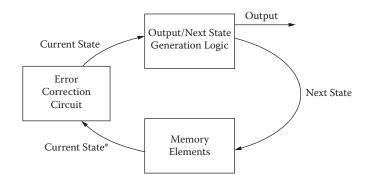

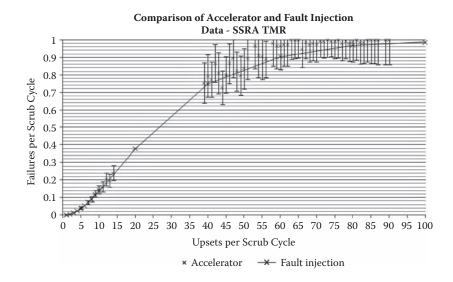

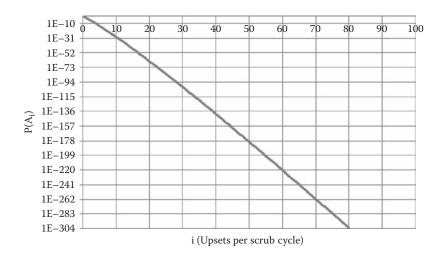

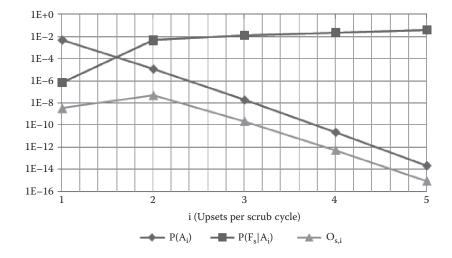

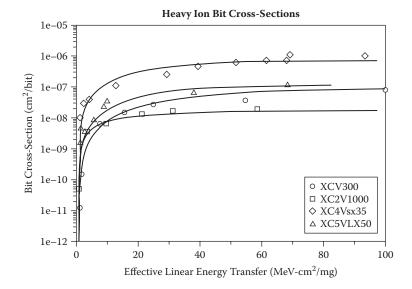

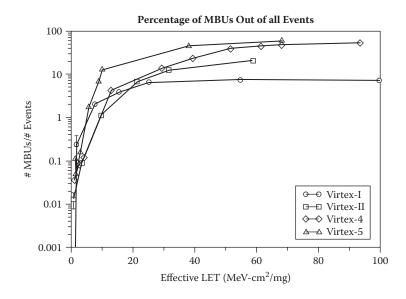

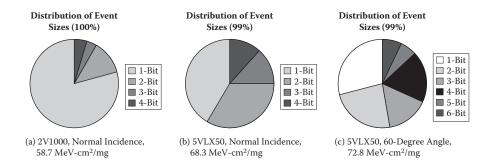

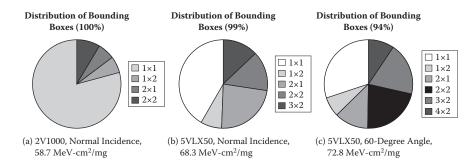

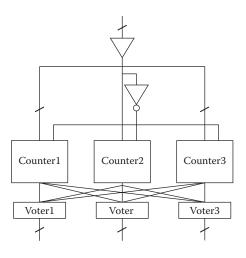

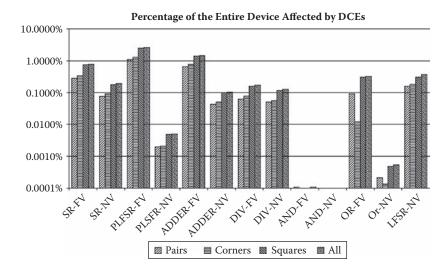

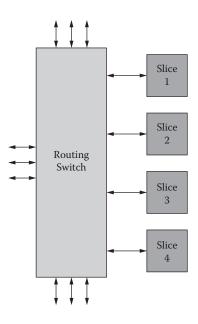

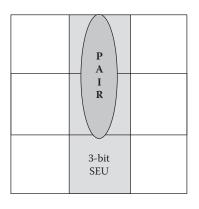

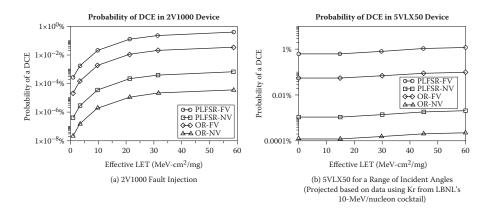

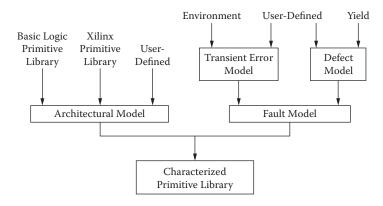

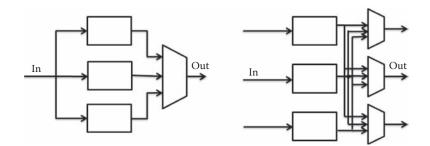

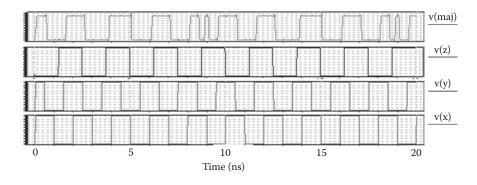

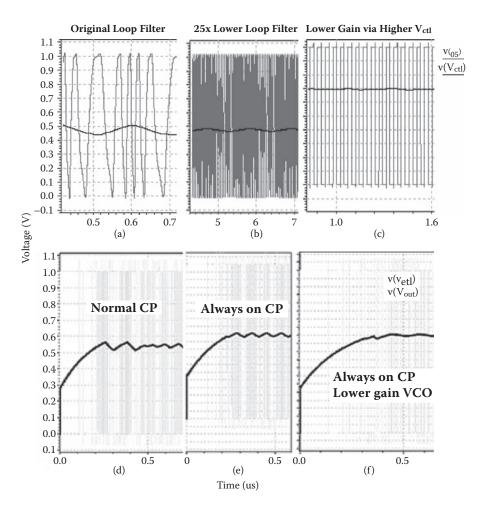

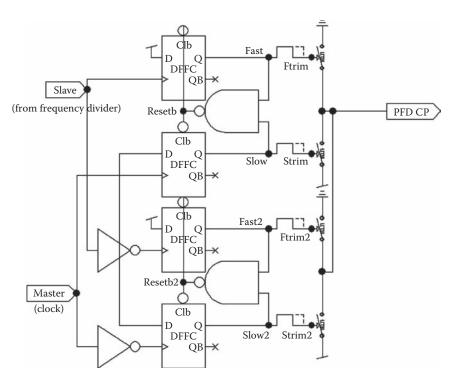

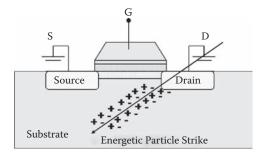

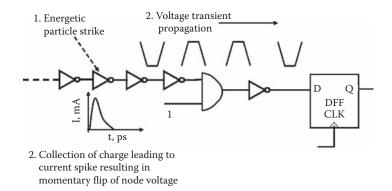

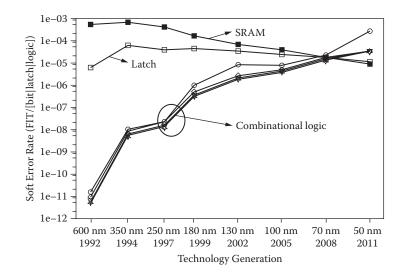

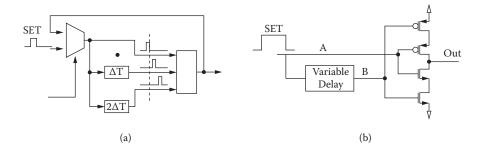

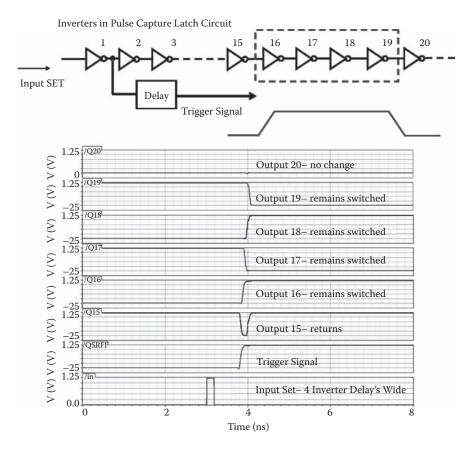

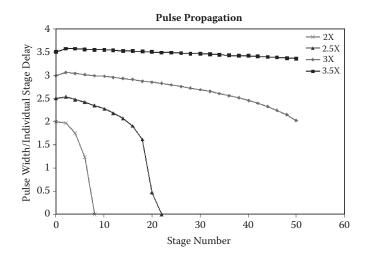

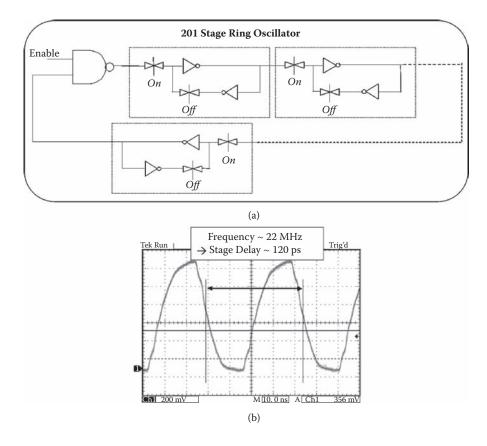

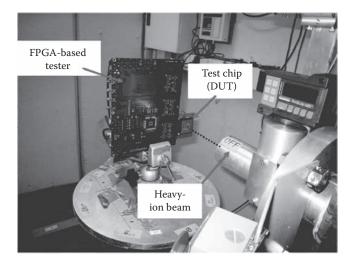

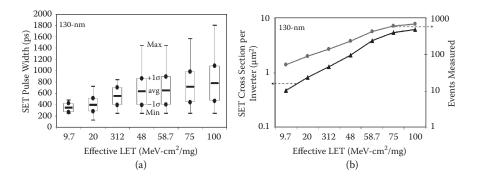

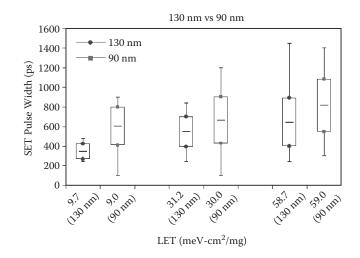

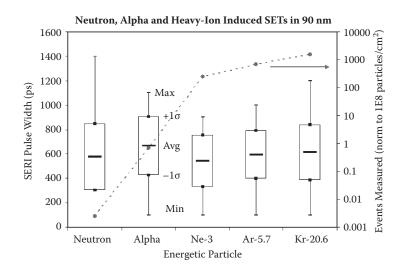

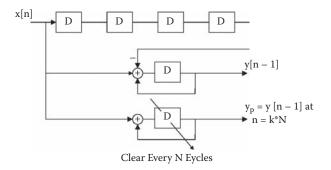

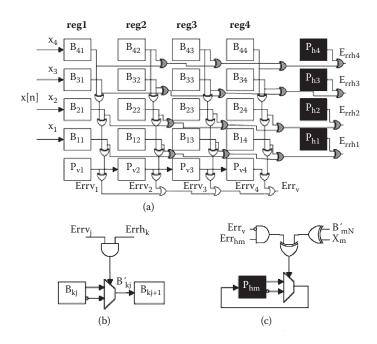

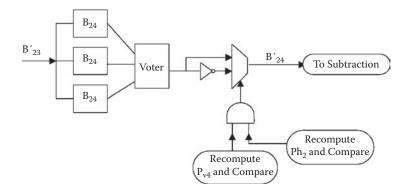

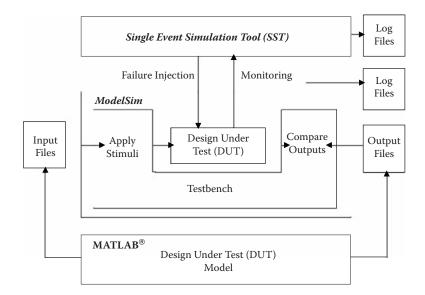

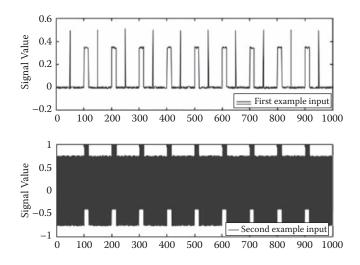

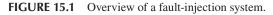

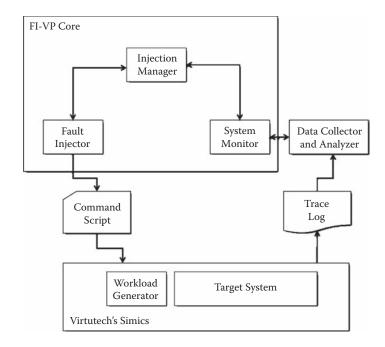

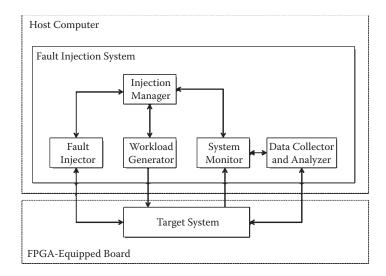

- F. Lemeilleur, M. Glaser, E.H.M. Heijne, P. Jarron, C. Soave, C. Leroy, et al., "Neutron, proton, and gamma irradiations of silicon detectors," *IEEE Trans. Nucl. Sci.* vol. 41, no. 3, 1994, pp. 425–431.