OF MISA Library

18EE34

hird Semester B.E. Degree Examination, June/July 2024 **Analog Electronic Circuits**

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

- With a neat circuit diagram and waveforms explain simple positive series clipper. Also draw the transfer characteristics. (10 Marks)

- b. What is biasing? What are the requirements of biasing circuits? With neat circuit diagram explain Emitter stabilized bias circuit.

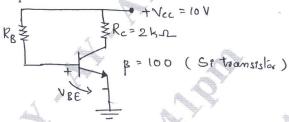

The circuit shown in Fig.Q2(a), for  $R_B=300~k\Omega$  and  $R_B=150~k\Omega$ , calculate  $I_B$ ,  $I_C$  and  $V_{CE}$ and determine region of operation.

Fig.Q2(a)

(10 Marks)

- Derive stability factors for fixed bias circuit:

- i) S<sub>(Ico)</sub>

- ii) S<sub>(VBE)</sub>

- iii)  $S_{(\beta)}$

- Draw and explain switching characteristics of transistor.

- (06 Marks)

- (04 Marks)

## Module-2

Derive expressions for A<sub>v</sub>, Z<sub>i</sub> and Z<sub>0</sub> of voltage divider bias circuit using hybrid model. 3

(10 Marks)

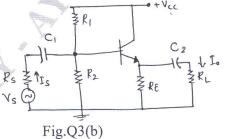

A common collector circuit shown in Fig.Q3(b) has following components:  $R_1 = 27k\Omega$ ,  $R_2 = 27k\Omega$ ,  $R_E = 5.6k\Omega$ ,  $R_L = 47k\Omega$ ,  $R_S = 600\Omega$ . The transistor parameters are  $h_{ie} = 1 \text{ k}\Omega$ ,  $h_{fe} = 85 \text{ and } h_{oe} = 2 \text{ } \mu\text{A/V}$ . Calculate (i)  $A_i$ (iii) A<sub>v</sub>

(v)

$$A_{vs} = \frac{V_0}{V_s}$$

(vi)  $A_i = \frac{I_0}{I_s}$

(10 Marks)

OR

State and prove Miller's theorem.

(10 Marks)

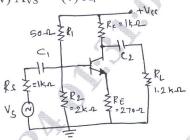

b. Fig.Q4(b) shows a single stage CE amplifier with unbypassed emitter resistance. Find

(iii) A<sub>v</sub> (iv) A<sub>VS</sub> (ii) R<sub>i</sub> (i) A<sub>i</sub>

Fig.Q4(b)

(10 Marks)

Module-3

Explain need for cascading of amplifiers.

voltage shunt feedback amplifier

(04 Marks)

Explain with a neat block diagram Two stage cascaded amplifier.

(06 Marks)

Derive  $A_i$ ,  $Z_0$  and  $A_V$  for Darlington Emitter follower.

(10 Marks)

OR

Explain with neat block diagram concept of feedback amolifier. (10 Marks) 6 Derive the expression for output resistance for a voltage series feedback amplifier and

(10 Marks)

Module-4

- Explain with neat circuit diagram transformer coupled class A amplifier. Derive equation for 7 (10 Marks) maximum efficiency.

- Explain classification of Power amplifiers. b.

(10 Marks)

Explain with neat circuit diagram R-C phase shift oscillator. 8

(10 Marks)

b. In a Wein bridge oscillator  $R_1 = R_2 = 100 k\Omega$  and ganged variable capacitor has a range from 50 pF to 500 pF. Find the range of frequency of the oscillations possible. If the frequency derived is 50 k\O more than the maximum frequency calculated above, find the value of (10 Marks) resistance to be connected in parallel with 100 k $\Omega$ .

Module-5

- Explain construction of n-channel JFET and also explain the working principle.

- The p-channel FET has a  $|I_{DSS}|$  = -12 mA ;  $|V_p|$  = 5V,  $V_{GS}$  is 5.32V. Calculate  $I_D$  ,  $g_m$ (10 Marks) and gmo.

OR

- With neat diagram explain constructional details of P-channel depletion type MOSFET and 10 (10 Marks) also explain its working.

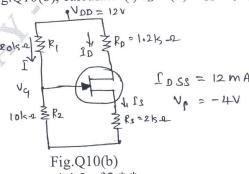

- b. For the circuit shown in Fig.Q10(b), calculate (i)  $I_D$  (ii)  $V_{GS}$  (iii)  $V_G$  (iv)  $V_{DS}$  (v)  $V_s$

(10 Marks)